#### Network Processor: Architecture and Applications

Yan Luo Yan Luo@uml.edu http://faculty.uml.edu/yluo/

## Outline

Overview of Network Processors

Network Processor Architectures

Applications

Case Studies

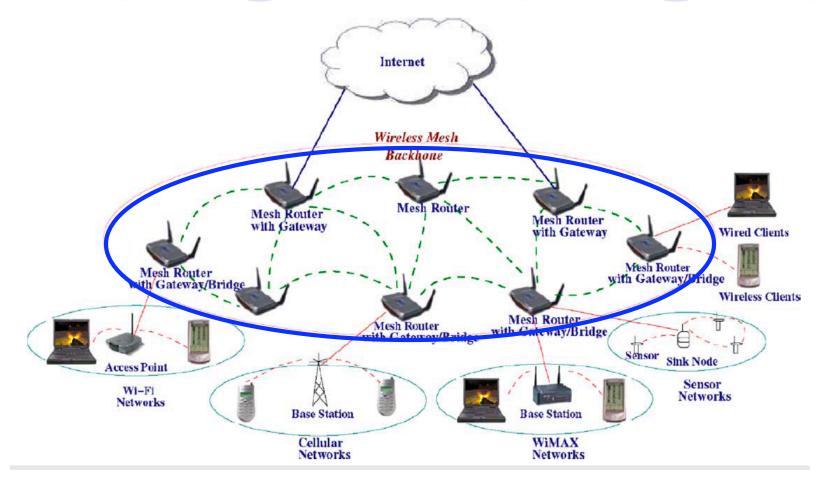

Wireless Mesh Network

a Content-Aware Switch

Conclusion

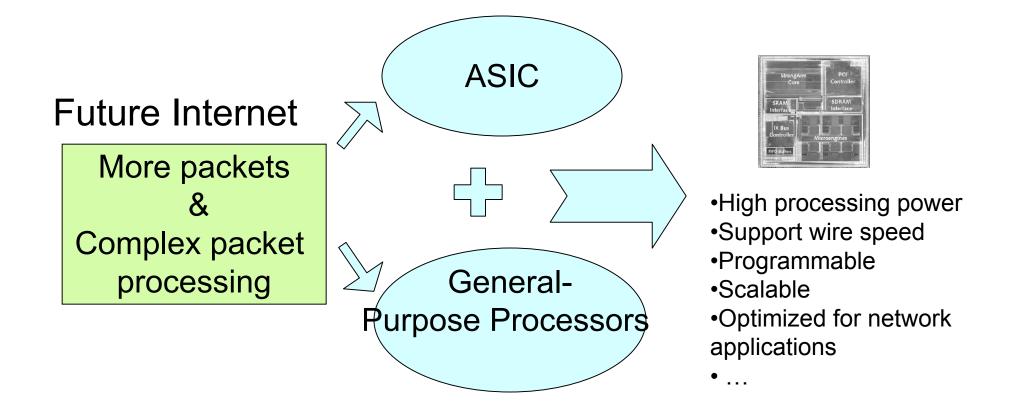

#### Packet Processing in the Future Internet

#### What is Network Processor ?

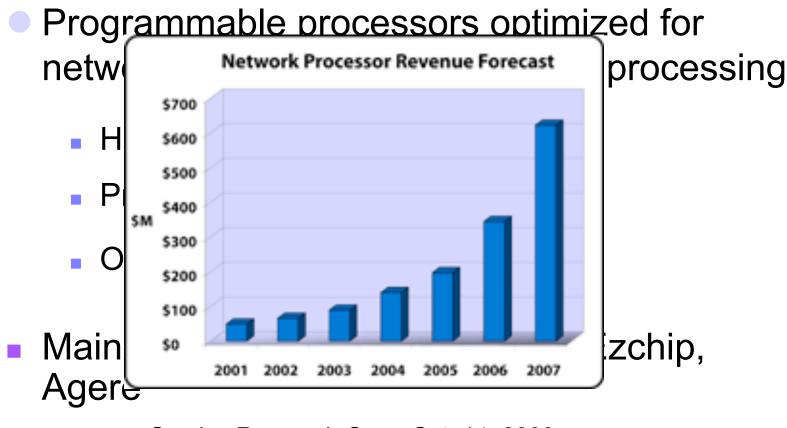

Semico Research Corp. Oct. 14, 2003

Yan Luo, CAR of UML

#### **Commercial Network Processors**

| Vendor | Product     | Line<br>speed      | Features                                                      |

|--------|-------------|--------------------|---------------------------------------------------------------|

| AMCC   | nP7510      | OC-192/<br>10 Gbps | Multi-core, customized ISA, multi-tasking                     |

| Intel  | IXP2850     | OC-192/<br>10 Gbps | Multi-core, h/w multi-threaded, coprocessor, h/w accelerators |

| Hifn   | 5NP4G       | OC-48/<br>2.5 Gbps | Multi-threaded multiprocessor complex, h/w accelerators       |

| EZchip | NP-2        | OC-192/<br>10 Gbps | Classification engines, traffic managers                      |

| Agere  | PayloadPlus | OC-192/<br>10 Gbps | Multi-threaded, on-chip traffic management                    |

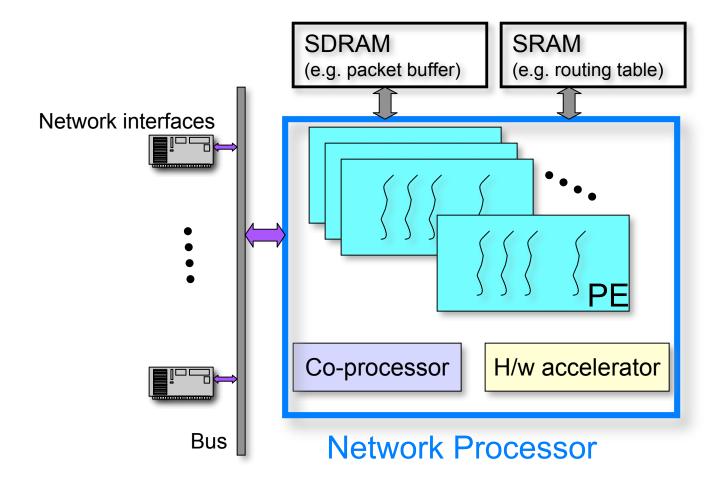

#### **Typical Network Processor Architecture**

#### Intel IXP2400 Network Processor

## Snapshots of IXP2xxx Based Systems

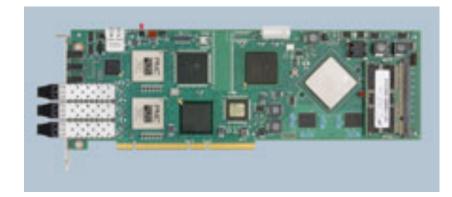

#### Radisys ENP2611 PCI Packet Processing Engine

- ADI Roadrunner Platform

- •IPv4 Forwarding/NAT

- •Forwarding w/ QoS / DiffServ

- •ATM RAN

- •IP RAN

- •IPv6/v4 dual stack forwarding

- •multiservice switches,

- •routers, broadband access devices,

- •intrusion detection and prevention (IDS/IPS)

- •Voice over IP (VoIP) gateway

- •Virtual Private Network gateway

- Content-aware switch

12/18/05

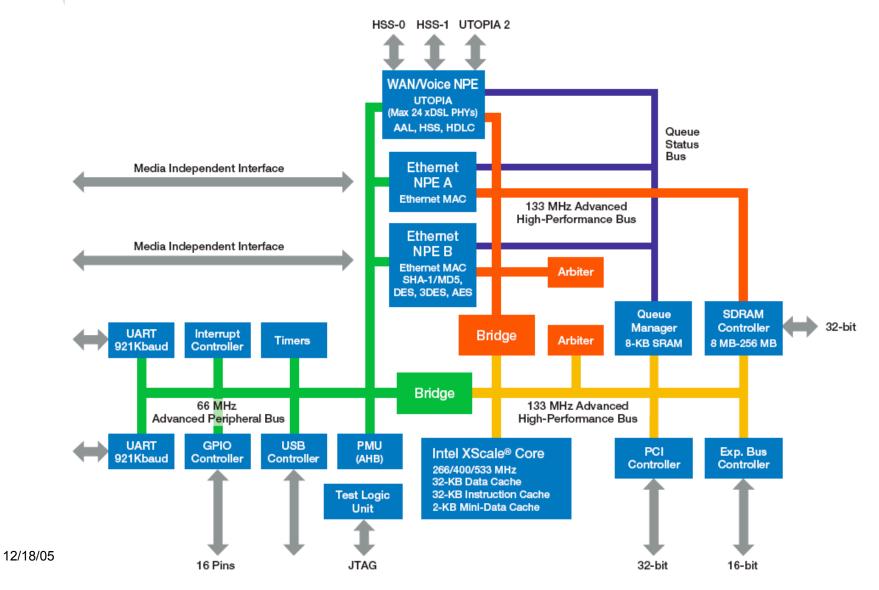

#### Intel IXP425 Network Processor

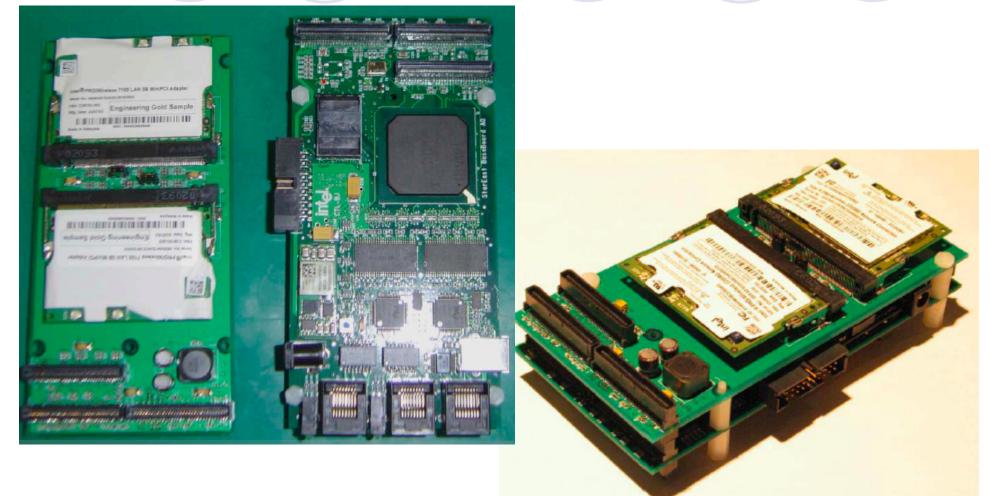

# StarEast: IXP425 Based Multi-radio Platform

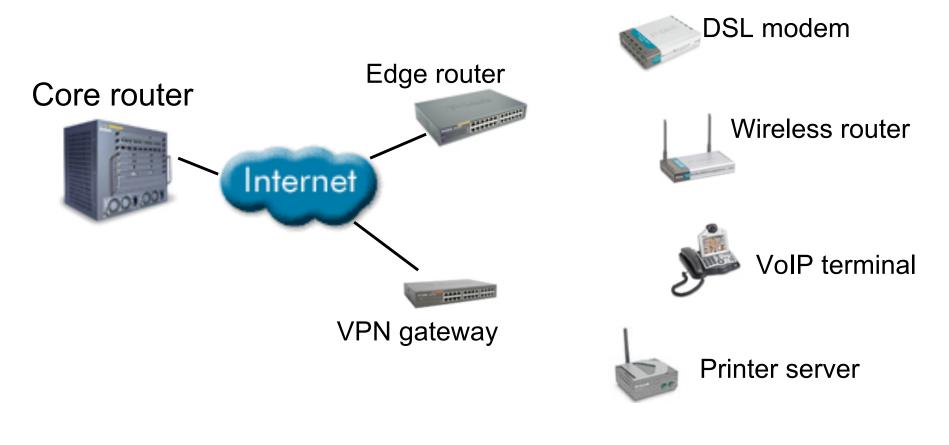

#### **Applications of Network Processors**

### Case Study 1: Wireless Mesh Network

## Software Stack on StarEast

|     | Customer Applications                      |            |           |                   |                                                 |        |                 |        |

|-----|--------------------------------------------|------------|-----------|-------------------|-------------------------------------------------|--------|-----------------|--------|

|     | Seamless Networking                        |            | Mesh      |                   | <b>Cognitive Radio</b><br>Radio Network Middlev |        | ware            |        |

|     | ARA/RAL (Radio/MAC Abstraction Layer) User |            |           |                   |                                                 |        |                 |        |

|     | IXP42                                      | 5 Access L | ibrary    | Cardbus           | minifCliffCl                                    | m      | iniPCI          | Kərnəl |

|     | NPE A                                      | NPE B      | USB Slave | Netgear<br>WAG511 | IntellFRO 100                                   | Prism2 | Driver     Card |        |

|     | Bootloader(Redboot)                        |            |           |                   |                                                 |        |                 |        |

|     | NPE A NPE B UART Intel PRO100              |            |           |                   |                                                 |        |                 |        |

|     | Stareast Hardware Platform                 |            |           |                   |                                                 |        |                 |        |

| 8/0 | 3/05 Yan Luo, CAR of UML                   |            |           |                   |                                                 |        |                 |        |

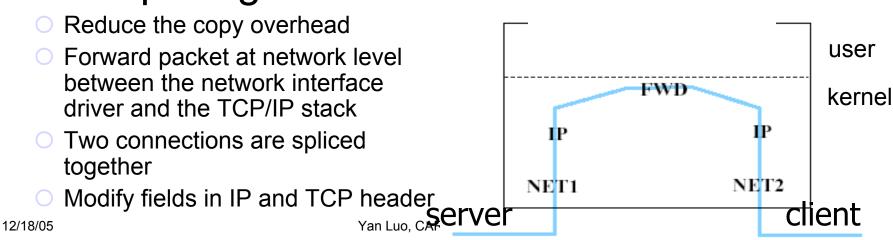

## Case Study 2: Content-aware Switch

- Front-end of a Web cluster, only one Virtual IP

- Route packets based on Layer 5 information

Examine application data in addition to IP& TCP

- Advantages over layer 4 switches

- Better load balancing: distributed based on content type

- Faster response: exploit cache affinity

- Better resource utilization: partition database

# Mechanisms to Build a Content-aware Switch

#### TCP gateway

- An application level proxy

- Setup 1<sup>st</sup> connection w/ client, parses request →server, setup 2<sup>nd</sup> connection w/ server

- Copy overhead

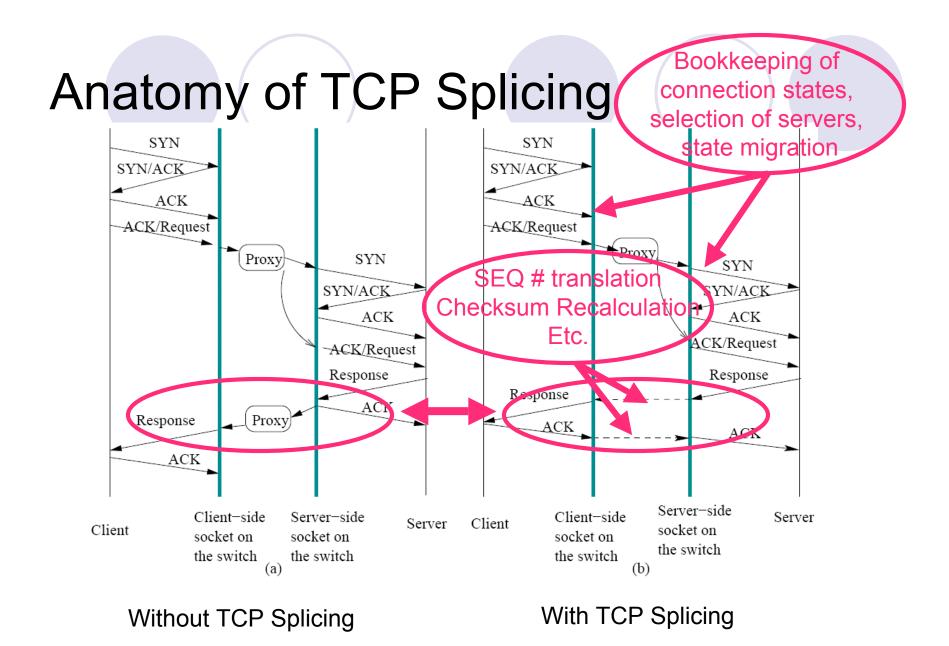

#### TCP splicing

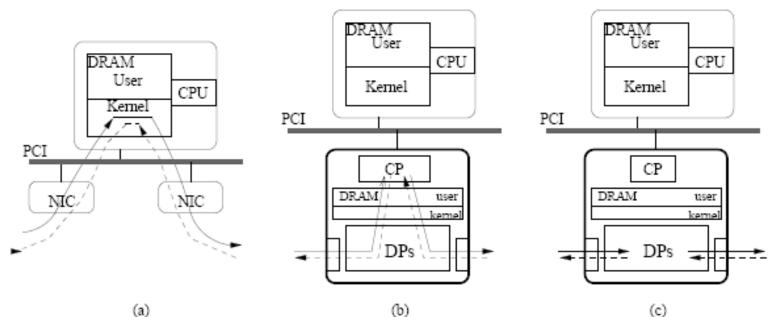

## **Design** Options

•Option 0: GP-based (Linux-based) switch

•Option 1: CP setup & and splices connections, DPs process packets sent after splicing

Connection setup & splicing is more complex than data forwarding

Packets before splicing need to be passed through DRAM queues

•Option 2: DPs handle connection setup, splicing & forwarding

12/18/05

Yan Luo, CAR of UML

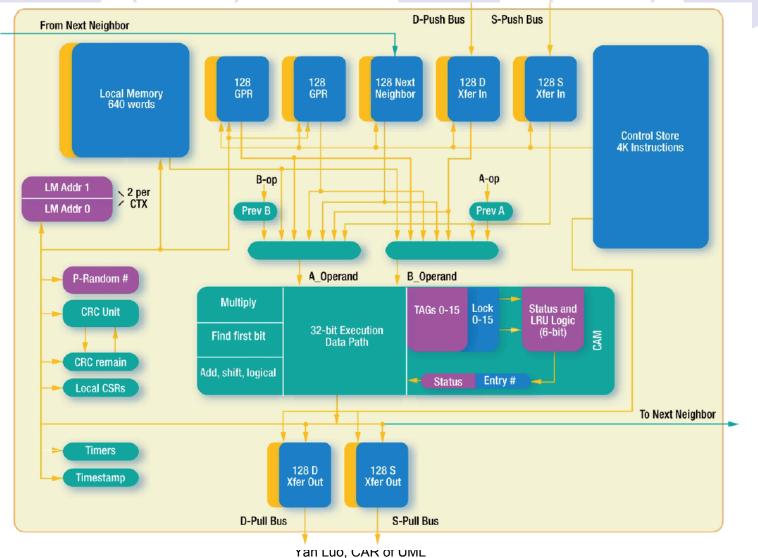

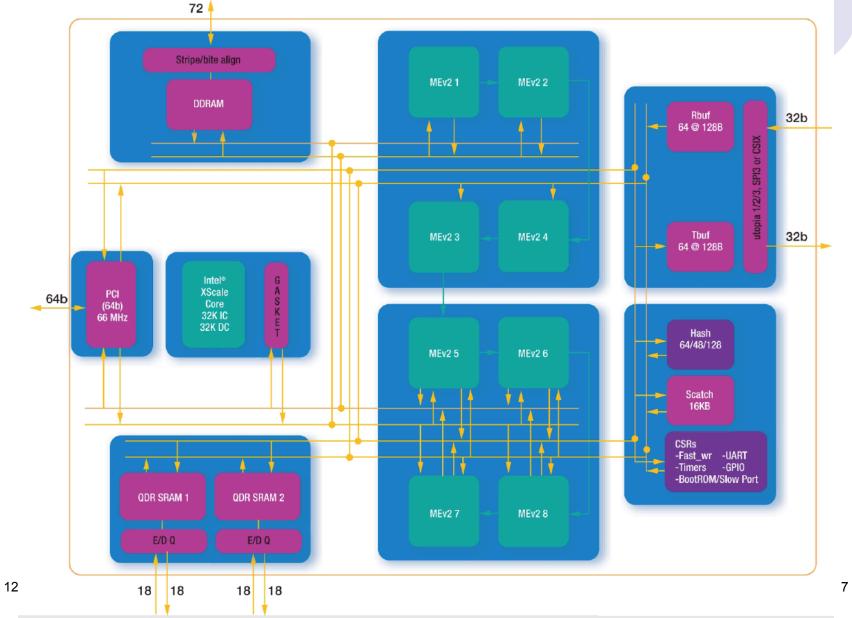

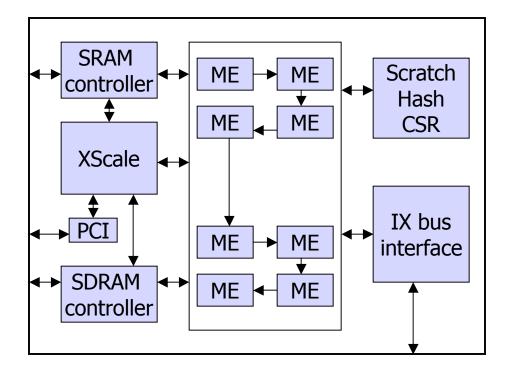

## IXP 2400 Block Diagram

- XScale core

- Microengines(MEs)

- 2 clusters of 4 microengines each

- Each ME

- run up to 8 threads

- 16KB instruction store

- Local memory

- Scratchpad memory, SRAM & DRAM controllers

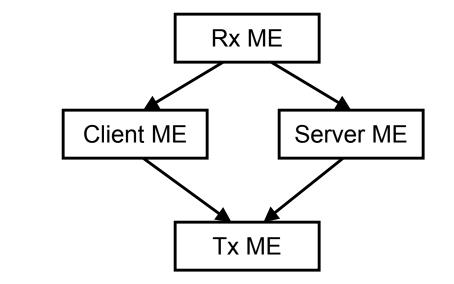

#### **Resource** Allocation

#### SRAM (8MB)

- Client side CB list

- Server side CB list

- server selection table

- Locks

DRAM (256MB)

Packet buffer

Scratchpad (16KB)

Packet queues

Client-side control block list

- record states for connections between clients and SpliceNP, states after splicing

- Server-side control block list

- record states for connections between server and SpliceNP

Microengines

## Comparison of Functionality • A lite version of TCP due to the limited instruction size of microengines.

Processing a SYN packet

| Ste<br>p              | Functionality                                                    | TCP | Linux<br>Splicer | SpliceNP                      |

|-----------------------|------------------------------------------------------------------|-----|------------------|-------------------------------|

| 1                     | Dequeue packet                                                   | Y   | Y                | Y                             |

| 2                     | IP header verification                                           | Y   | Y                | Y                             |

| 3                     | IP option processing                                             | Υ   | Υ                | Ν                             |

| 4                     | TCP header verification                                          | Y   | Y                | Y                             |

| 5                     | Control block lookup                                             | Y   | Y                | Y                             |

| 6                     | Create new socket and set state to LISTEN                        | Y   | Y                | No socket, only control block |

| 7                     | Initialize TCP and IP header template                            | Y   | Υ                | Ν                             |

| 8                     | Reset idle time and keep-alive timer                             | Υ   | Υ                | Ν                             |

| 9                     | Process TCP option                                               | Y   | Y                | Only MSS<br>option            |

| <b>10</b><br>12/18/05 | Send ACK packet, change state to<br>SYN_RCVD Yan Luo, CAR of UML | Y   | Y                | Y 20                          |

#### Experimental Setup

Radisys ENP2611 containing an IXP2400

- XScale & ME: 600MHz

- 8MB SRAM and 128MB DRAM

- Three 1Gbps Ethernet ports: 1 for Client port and 2 for Server ports

- Server: Apache web server on an Intel 3.0GHz Xeon processor

- Client: Httperf on a 2.5GHz Intel P4 processor

- Linux-based switch

- Loadable kernel module

- 2.5GHz P4, two 1Gbps Ethernet NICs

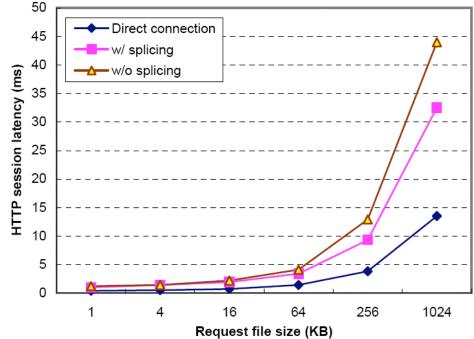

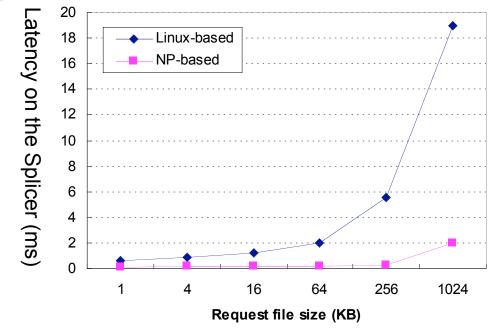

## Latency on a Linux-based TCP Splicer

#### Latency is reduced by TCP splicing

#### Latency vs Request File Size

## Latency reduced significantly ○ 83.3% (0.6ms → 0.1ms) @ 1KB

The larger the file size, the higher the reduction

89.5% @ 1MB file

# Comparison of Packet Processing Latency

| Packet  |             | IXP2        | 2400         | Linux        | Latency   |

|---------|-------------|-------------|--------------|--------------|-----------|

| Туре    |             | Microengine | Latency (us) | Latency (us) | reduction |

| Control | SYN         | clientME    | 7.2          | 48           | 85%       |

| Packet  | ACK/Request | clientME    | 8.8          | 52           | 83%       |

|         | SYN/ACK     | serverME    | 8.5          | 42           | 80%       |

| Data    | Data        | serverME    | 6.5          | 13.6         | 52%       |

| Packet  | ACK         | clientME    | 6.5          | 13.6         | 52%       |

Table 5: Processing latency for control and data packets

## Analysis of Latency Reduction

| Linux-based                        | NP-based             |

|------------------------------------|----------------------|

| Interrupt: NIC raises an interrupt | polling              |

| once a packet comes                |                      |

| NIC-to-mem copy                    | No copy: Packets     |

| Xeon 3.0Ghz Dual processor w/      | are processed inside |

| 1Gbps Intel Pro 1000 (88544GC)     | without two copies   |

| NIC, 3 us to copy a 64-byte packet |                      |

| by DMA                             |                      |

| Linux processing: OS overheads     | IXP processing:      |

| Processing a data packet in        | Optimized ISA        |

| splicing state: 13.6 us            | 6.5 us               |

|                                    |                      |

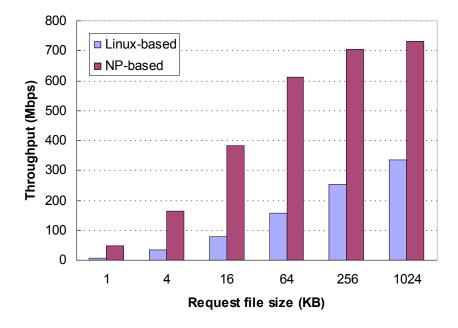

## Throughput vs Request File Size

- Throughput is increased significantly

- 5.7x for small file size @ 1KB, 2.2x for large file @ 1MB

- Higher improvement for small files

- Latency reduction for control packets > data packets

- Control packets take a larger portion for small files

### Conclusion

- Network Processor combines highperformance packet processing and programmability

- A large variety of NP applications

- Efficient resource utilization is challenging

## Thank you !

## Microengine

12/18/05