# Chapter 5

#### 8088/8086 Microprocessor Programming

#### Introduction

- 5.1 Data-Transfer Instructions—✓

- 5.2 Arithmetic Instructions—✓

- 5.3 Logic Instructions—

- 5.4 Shift Instructions—

- 5.5 Rotate Instructions —

|     |        |    | Instructions- | Move |

|-----|--------|----|---------------|------|

| Ins | tructi | on |               |      |

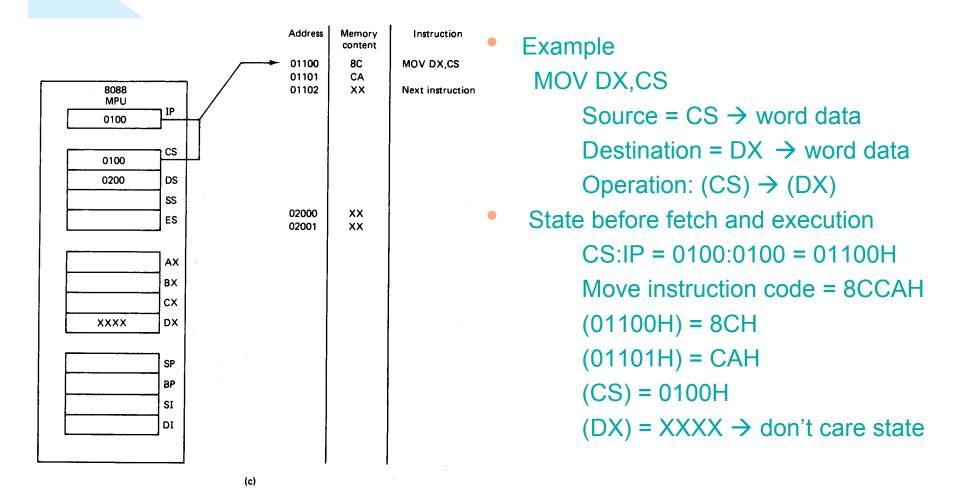

Move instruction

- Used to move (copy) data between:

- Registers

- Register and memory

- Immediate operand to a register or memory

- General format: MOV D,S

- Operation: Copies the content of the source to the destination

- $(S) \rightarrow (D)$

- Source contents unchanged

- Flags unaffected

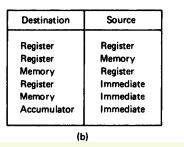

- Allowed operands

- Register

Memory

Accumulator (AH,AL,AX)

- Immediate operand (Source only) Segment register (Seg-reg)

- Examples:

MOV [SUM],AX (AL) → (address SUM) (AH) → (address SUM+1)

| Mnemonic | Meaning | Format  | Operation | Flags affected |

|----------|---------|---------|-----------|----------------|

| MOV      | Move    | MOV D,S | (S) → (D) | None           |

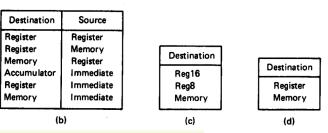

| Destination | Source      |

|-------------|-------------|

| Memory      | Accumulator |

| Accumulator | Memory      |

| Register    | Register    |

| Register    | Memory      |

| Memory      | Register    |

| Register    | Immediate   |

| Memory      | Immediate   |

| Seg-reg     | Reg16       |

| Seg-reg     | Mem16       |

| Reg16       | Seg-reg     |

| Memory      | Seq-req     |

(Ь)

1. Is the destination in a register or memory?

2. What is the addressing mode of the source?

- 3. The destination?

- 4. What is SUM?

Debug execution example MOV CX,[20] DS = 1A00 (DS:20) = AA55H (1A00:20) → (CX)

1. Where is the source operand located?

2. What is the addressing mode of the source operand?

C:\DOS>DEBUG  $-\dot{R}$ AX=0000 BX=0000 CX=0000 DX=0000 SP=FFEE BP=0000 SI=0000 DI=0000 DS=1342 ES=1342 SS=1342 CS=1342 IP=0100 NV UP EI PL NZ NA PO NC 1342:0100 OF DB OF -A 1342:0100 MOV CX,[20] 1342:0104 -R DS DS 1342 :1A00 -Transferration and the second s AX=0000 BX=0000 CX=AA55 DX=0000 SP=FFEE BP=0000 SI=0000 DI=0000 DS=1A00 ES=1342 SS=1342 CS=1342 IP=0104 NV UP EI PL NZ NA PO NC 1342:0104 FFF3 PUSH BX -Q C:\DOS>

MOV AX,2000H MOV DS, AX MOV ES, AX MOV AX,3000H MOV SS,AX MOV AX,0H MOV BX,AX MOV CX,0AH MOV DX,100H MOV SI,200H MOV DI,300H; init\_index\_reg

1. What addressing modes are in use in this program?

- Example—Initialization of internal registers with immediate data and address information

- DS, ES, and SS registers initialized from immediate data via AX

IMM16  $\rightarrow$  (AX)

$(AX) \rightarrow (DS) \& (ES) = 2000H$

$IMM16 \rightarrow (AX)$

$(AX) \rightarrow (SS) = 3000H$

• Data registers initialized IMM16  $\rightarrow$  (AX) =0000H

$(AX) \rightarrow (BX) = 0000H$

IMM16  $\rightarrow$  (CX) = 000AH and (DX) = 0100H

Index register initialized from immediate operations

IMM16  $\rightarrow$  (SI) = 0200H and (DI) = 0300H

| Mnemonic | Meaning  | Format   | Operation | Flags affected |

|----------|----------|----------|-----------|----------------|

| ХСНС     | Exchange | XCHG D,S | (D) ↔ (S) | None           |

(a)

| Destination | Source   |

|-------------|----------|

| Accumulator | Reg16    |

| Memory      | Register |

| Register    | Register |

| Register    | Memory   |

(b)

- 1. Why do you think this is known as a "complex instruction?"

- 2. How else could this operation be performed?

- 3. What is the benefit of using XCHG?

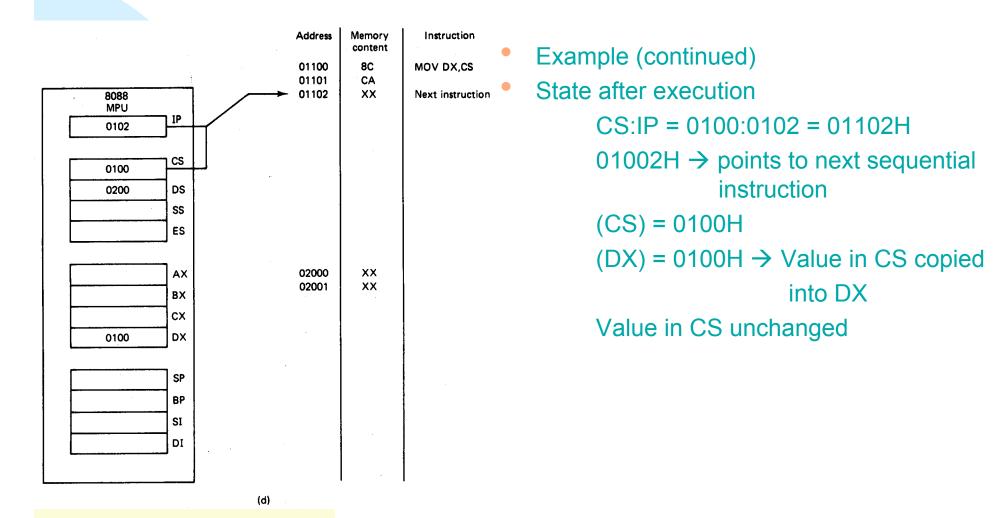

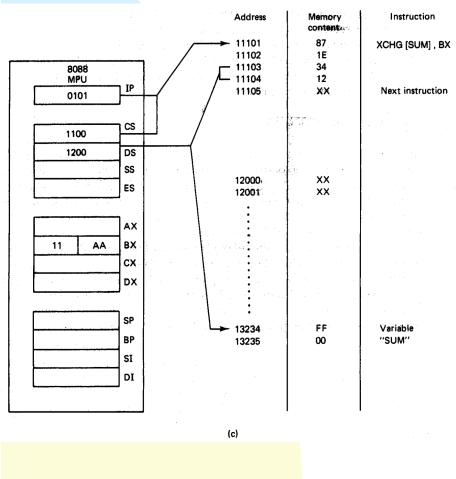

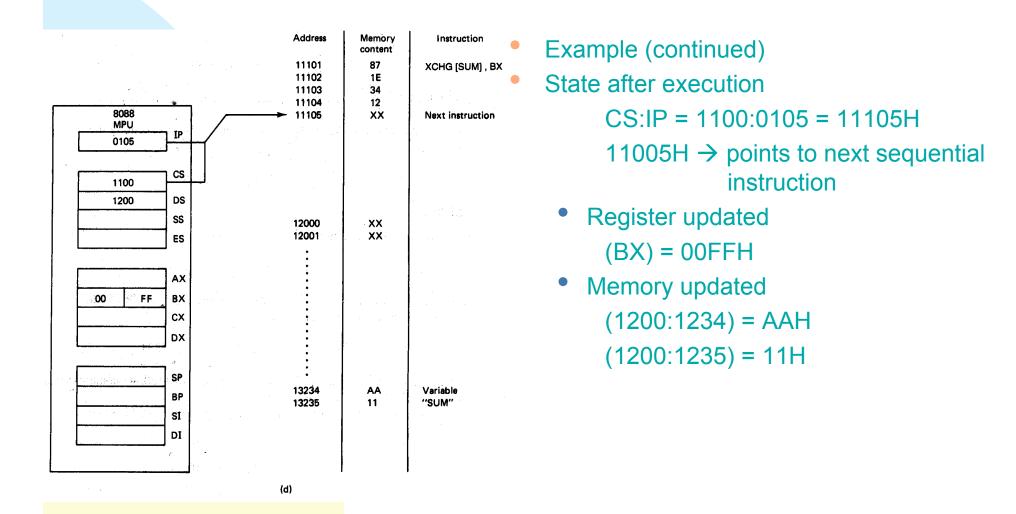

- Exchange instruction

- Used to exchange the data between two data registers or a data register and memory

- General format: XCHG D,S

- Operation: Swaps the content of the source and destination

- Both source and destination change

(S) → (D)

- $(D) \rightarrow (S)$

- Flags unaffected

- Special accumulator destination version executes faster

- Examples:

XCHG AX,DX (Original value in AX)  $\rightarrow$  (DX) (Original value in DX)  $\rightarrow$  (AX)

Example XCHG [SUM], BX Source =  $BX \rightarrow$  word data Destination = memory offset SUM  $\rightarrow$  word data Operation: (SUM)  $\rightarrow$  (BX)  $(BX) \rightarrow (SUM)$ What is the general logical address of the destination operand? State before fetch and execution CS:IP = 1100:0101 = 11101HMove instruction code = 871E3412H (01104H,01103H) = 1234H = SUM(DS) = 1200H(BX) = 11AA(DS:SUM) = (1200:1234) = 00FFHWhat is this type data organization The 8088 and 8086 Microprocessors Triebel and Singh Called? 9

#### Debug execution of example

| C:\DOS>DEBUG<br>−R                                         |                                         |                     |                                                    |

|------------------------------------------------------------|-----------------------------------------|---------------------|----------------------------------------------------|

| AX=0000 BX=0000 CX=<br>DS=1342 ES=1342 SS=<br>1342:0100 OF | =0000 DX=0000<br>=1342 CS=1342<br>DB 0F | SP=FFEE<br>IP=0100  | BP=0000 SI=0000 DI≠0000<br>NV UP EI PL NZ NA PO NC |

| -A 1100:101<br>1100:0101 XCHG [1234]                       | , BX                                    |                     |                                                    |

| 1100:0105<br>-R BX                                         |                                         |                     |                                                    |

| BX 0000                                                    |                                         |                     |                                                    |

| :11AA<br>-R DS                                             |                                         | •                   |                                                    |

| DS 1342<br>:1200                                           |                                         |                     |                                                    |

| -R CS<br>CS 1342                                           |                                         |                     |                                                    |

| :1100                                                      |                                         | ,                   |                                                    |

| -R IP<br>IP 0100                                           |                                         |                     |                                                    |

| :101<br>-R                                                 |                                         |                     |                                                    |

| AX=0000 BX=11AA CX=<br>DS=1200 ES=1342 SS=                 | =0000 DX=0000<br>=1342 CS=1100          | SP=FFEE<br>IP=0101  | BF=0000 SI=0000 DI=0000<br>NV UP EI PL NZ NA PO NC |

| 1100:0101 871E3412                                         | XCHG BX                                 | ,[1234]             | DS:1234=0000                                       |

| -E 1234 FF 00                                              |                                         |                     |                                                    |

| 1100:0101 871E3412<br>-T                                   | XCHG BX                                 | ,[1234]             |                                                    |

| AX=0000 BX=00FF CX                                         | =0000 DX=0000                           | SP=FFEE             | BP=0000 SI=0000 DI=0000                            |

|                                                            | =1342 CS=1100                           | IP=0105<br>P-02],AX | NV UP EI PL NZ NA PO NC<br>SS:FFFE=0000            |

| -D 1234 1235                                               | AA 11                                   |                     |                                                    |

| 1200:1230<br>-Q                                            | NN 11                                   | · .                 | ••                                                 |

| C:\DOS>                                                    |                                         |                     |                                                    |

|                                                            | 088 and 8086                            | 6 Micropro          | cessors, Triebel and Singh                         |

11

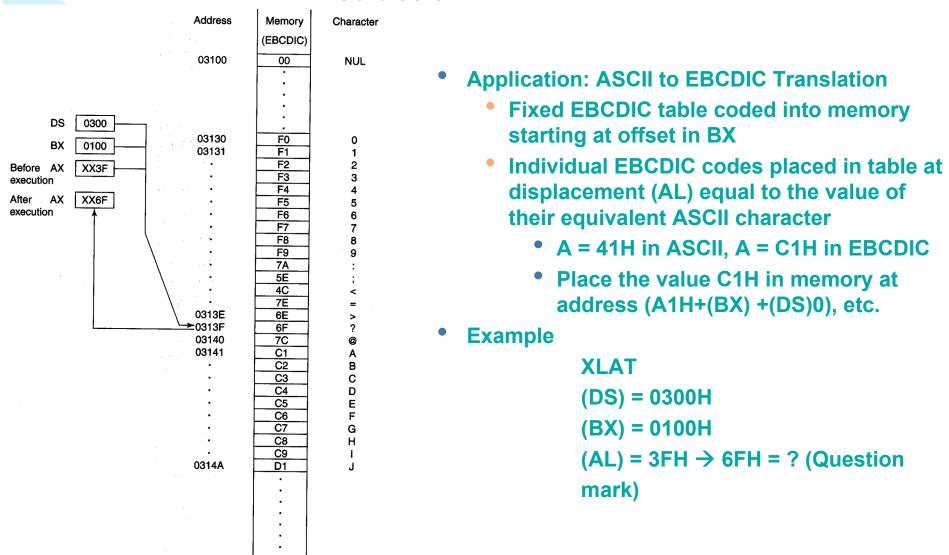

# 5.1 Data Transfer Instructions- Translate Instruction

| Mnemonic | Meaning   | Format | Operation                | Flags affected |

|----------|-----------|--------|--------------------------|----------------|

| XLAT     | Translate | XLAT   | ((AL)+(BX)+(DS)0) → (AL) | None           |

#### • Translate instruction

- Used to look up a byte-wide value in a table in memory and copy that value in the AL register

- General format:

#### **XLAT**

Operation: Copies the content of the element pointed to in the source table in memory to the AL register

$((AL)+(BX) + (DS)0) \rightarrow (AL)$

Where:

(DS)0 = Points to the active data segment

(BX) = Offset to the first element in the table

(AL) = Displacement to the element of the table that is to be accessed\*

\*8-bit value limits table size to 256 elements

### 5.1 Data Transfer Instructions- Translate Instruction

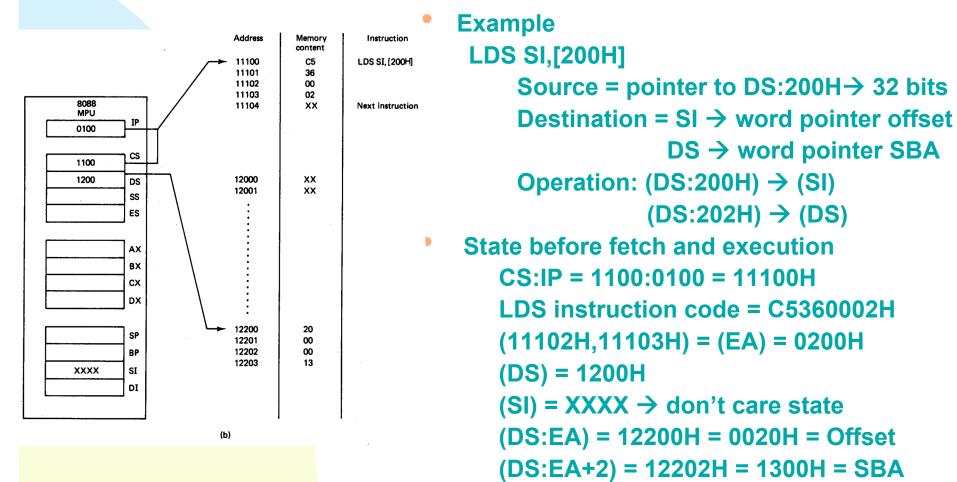

#### 5.1 Data Transfer Instructions- Load Effective Address and Load Full Pointer Instructions

| Mnemonic | Meaning                | Format          | Operation                             | Flags affected |

|----------|------------------------|-----------------|---------------------------------------|----------------|

| LEA      | Load effective address | LEA Reg16,EA    | EA → (Reg16)                          | None           |

| LDS      | Load register and DS   | LDS Reg16,Mem32 | (Mem32) → (Reg16)<br>(Mem32+2) → (DS) | None           |

| LES      | Load register and ES   | LES Reg16,Mem32 | (Mem32) → (Reg16)<br>(Mem32+2) → (ES) | None           |

(a)

- Load effective address instruction

- Used to load an address pointer offset from memory into a register

- General format: LEA Reg16,EA

- Operation:

- $(EA) \rightarrow (Reg16)$

- Source unaffected:

- Flags unaffected

#### Load full pointer

- Used to load a full address pointer from memory into a segment register and a register

- Segment base address

- Offset

- General format and operation for LDS

- LDS Reg16,EA

$(EA) \rightarrow (Reg16)$

(EA+2) →(DS)

The 8088 and 8086 Microprocess ES operates the same, except 14 initializes ES

#### 5.1 Data Transfer Instructions- Load Effective Address and Load Full Pointer Instructions

#### 5.1 Data Transfer Instructions- Load Effective Address and Load Full Pointer Instructions

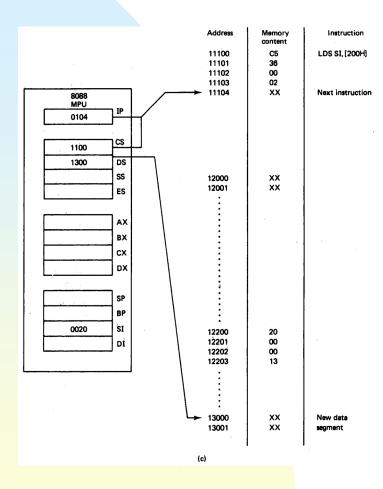

Example (continued)

#### State after execution

CS:IP = 1100:0104 = 11104H

01004H → points to next sequential instruction

$(DS) = 1300H \rightarrow defines a new data$

segment

(SI) = 0020H  $\rightarrow$  defines new offset

into DS

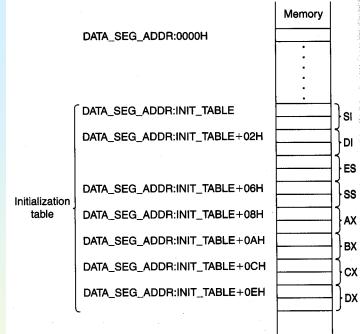

#### 5.2 Data Transfer Instructions- Load Effective Address and Load Full Pointer Instructions

MOV AX, DATA\_SEG\_ADDR MOV DS,AX MOV SI,[INIT\_TABLE] LES DI,[INIT\_TABLE+02H] MOV AX,[INIT\_TABLE+06H] MOV SS,AX MOV AX,[INIT\_TABLE+08H] MOV BX,[INIT\_TABLE+0AH] MOV CX,[INIT\_TABLE+0CH] MOV DX,[INIT\_TABLE+0EH] Example—Initialization of internal registers from memory with data and address information

DS loaded via AX with immediate value using move instructions

DATA\_SEG\_ADDR  $\rightarrow$  (AX)  $\rightarrow$  (DS)

- Index register SI loaded with move from table (INIT\_TABLE,INIT\_TABLE+1) → SI

- DI and ES are loaded with load full pointer instruction

(INIT\_TABLE+2,INIT\_TABLE+3) → DI (INIT\_TABLE+4,INIT\_TABLE+5) → ES

• SS loaded from table via AX using move instructions

(INIT\_TABLE+6,INIT\_TABLE+7)  $\rightarrow$  AX  $\rightarrow$  (SS)

• Data registers loaded from table with move instructions

$(INIT_TABLE+8, INIT_TABLE+9) \rightarrow AX$

$(INIT_TABLE+A, INIT_TABLE+B) \rightarrow BX$

```

(INIT_TABLE+C, INIT_TABLE+D) \rightarrow CX

```

```

(INIT TABLE+E, INIT TABLE+F) \rightarrow DX

```

| Mnemonic | Meaning                     | Format   | Operation                                                      | Flags Affected                       |

|----------|-----------------------------|----------|----------------------------------------------------------------|--------------------------------------|

| ADD      | Addition                    | ADD D, S | $(S) + (D) \rightarrow (D)$<br>Carry $\rightarrow (CF)$        | OF, SF, ZF, AF, PF, CF               |

| ADC      | Add with carry              | ADC D, S | $(S) + (D) + (CF) \rightarrow (D)$<br>Carry $\rightarrow (CF)$ | OF, SF, ZF, AF, PF, CF               |

| INC      | Increment by 1              | INC D    | $(D) + 1 \rightarrow (D)$                                      | OF, SF, ZF, AF, PF                   |

| ААА      | ASCII adjust for addition   | AAA      |                                                                | AF, CF<br>OF, SF, ZF, PF undefined   |

| DAA      | Decimal adjust for addition | DAA      |                                                                | SF, ZF, AF, PF, CF,<br>OF, undefined |

(a)

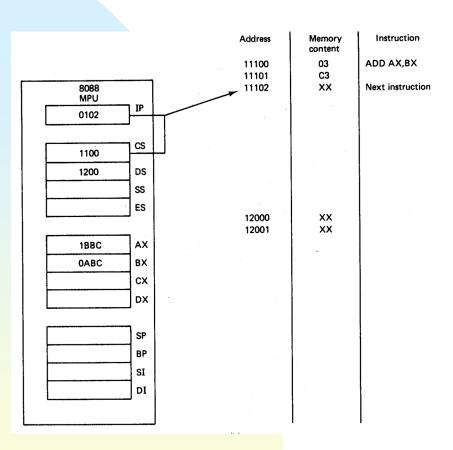

| Destination |   |

|-------------|---|

| Reg16       |   |

| Reg8        |   |

| Memory      |   |

|             | ┛ |

(c)

- Variety of arithmetic instruction provided to support integer addition—core instructions are

- ADD→ Addition

- ADC  $\rightarrow$  Add with carry

- INC  $\rightarrow$  Increment

- Addition Instruction—ADD

- ADD format and operation: ADD D,S

- $(S) + (D) \rightarrow (D)$

- Add values in two registers ADD AX,BX

- $(AX) + (BX) \rightarrow (AX)$

- Add a value in memory and a value in a register

ADD [DI],AX

$(DS:DI) + (AX) \rightarrow (DS:DI)$

- Add an immediate operand to a value in a register or memory

ADD AX 100H

- ADD AX,100H

$(AX) + IMM16 \rightarrow (AX)$

- Flags updated based on result

- CF, OF, SF, ZF, AF, PF

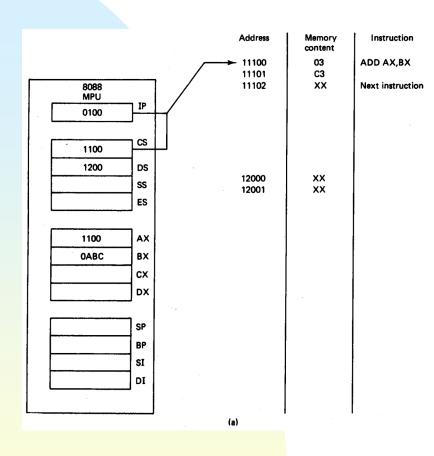

Example ADD AX,BX

$(\mathsf{AX}) + (\mathsf{BX}) \rightarrow (\mathsf{AX})$

- Word-wide register to register add

- Half adder operation

- State before fetch and execution CS:IP = 1100:0100 = 11100HADD machine code = 03C3H (AX) = 1100H (BX) = 0ABCH (DS) = 1200H(1200:0000) = 12000H = XXXX

- Example (continued)

- State after execution

- CS:IP = 1100:0102 = 11102H

- 11102H → points to next sequential instruction

- Operation performed (AX) + (BX)  $\rightarrow$  (AX)

- $(1100H) + (0ABCH) \rightarrow 1BBCH$

- (AX) = 1BBCH

- = 0001101110111100<sub>2</sub>

- (BX) = unchanged

- Impact on flags

- CF = 0 (no carry resulted)

- ZF = 0 (not zero)

- SF = 0 (positive)

- PF = 0 (odd parity)—parity flag is only based on the bits of the least significant byte

| Mnemonic | Meaning                     | Format   | Operation                                                      | Flags Affected                       |

|----------|-----------------------------|----------|----------------------------------------------------------------|--------------------------------------|

| ADD      | Addition                    | ADD D, S | $(S) + (D) \rightarrow (D)$<br>Carry $\rightarrow (CF)$        | OF, SF, ZF, AF, PF, CF               |

| ADC      | Add with carry              | ADC D, S | $(S) + (D) + (CF) \rightarrow (D)$<br>Carry $\rightarrow (CF)$ | OF, SF, ZF, AF, PF, CF               |

| INC      | Increment by 1              | INC D    | $(D) + 1 \rightarrow (D)$                                      | OF, SF, ZF, AF, PF                   |

| AAA      | ASCII adjust for addition   | AAA      |                                                                | AF, CF<br>OF, SF, ZF, PF undefined   |

| DAA      | Decimal adjust for addition | DAA      |                                                                | SF, ZF, AF, PF, CF,<br>OF, undefined |

- Add with carry instruction—ADC

- ADC format and operation: ADC D,S

- $(S) + (D) + (CF) \rightarrow (D)$

- Full-add operation

- Used for extended addition

- Add two registers with carry ADC AX,BX

(AX) + (PX) + (CE) -> (AX)

$(AX) + (BX) + (CF) \rightarrow (AX)$

- Add register and memory with carry ADC [DI],AX

- $(DS:DI) + (AX) + (CF) \rightarrow (DS:DI)$

- Add immediate operand to a value in a register or memory

ADC AX,100H

$(AX) + IMM16 + (CF) \rightarrow (AX)$

- Same flags updated as ADD

- Increment instruction—INC

- INC format and operation

INC D

$(D) + 1 \rightarrow (D)$

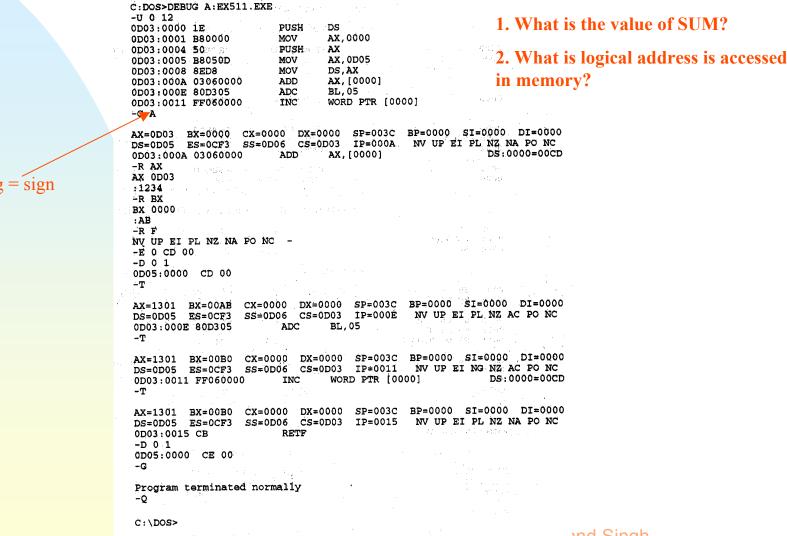

- Example—Arithmetic computations

- Initial state:

- (AX) = 1234H (BL) = ABH (SUM) = 0000

- (SUM) = 00CDH (CF) = 0

- (<u>IM) (CF)</u> Op

- Instruction (AX) (BL) (SUM) Initial state 1234 AB 00CD 0 ADD AX, [SUM] 1301 AB 00CD 0 ADC BL, 05H 1301 B0 00CD 0 INC WORD PTR [SUM] 1301 B0 00CE 0

- 1. Does the column (SUM) stand for a value in a register code memory, or a storage location in memory?

- 2. Why is the operand of the INC instruction preceded by WORD PTR?

- Operation of first instruction (DS:SUM) + (AX) → (AX)

00CDH + 1234H = 1301H (AX) = 1301H

- (CF) = unchanged

- Operation of second instruction

(BL) + IMM8 +(CF) → BL

- ABH + 05H + 0 = B0H

- (BL) = B0H

- (CF) = unchanged

- Operation of third instruction (DS:SUM) + 1 → (DS:SUM) 00CDH + 1 = 00CEH (SUM) = 00CEH (CF) = unchanged

Example—Execution of the arithmetic computation sequence

The oboo and oboo whereprocessors, theber and Singh

Missing = sign

## 5.2 Arithmetic Instructions- Subtraction Instructions

| Mnemonic | Meaning                         | Format  | Operation                                                | Flags affected                     |

|----------|---------------------------------|---------|----------------------------------------------------------|------------------------------------|

| SUB      | Subtract                        | SUB D,S | $(D) - (S) \rightarrow (D)$<br>Borrow $\rightarrow$ (CF) | OF, SF, ZF, AF, PF, CF             |

| SBB      | Subtract with borrow            | SBB D,S | $(D) - (S) - (CF) \rightarrow (D)$                       | OF, SF, ZF, AF, PF, CF             |

| DEC      | Decrement by 1                  | DEC D   | $(D) - 1 \rightarrow (D)$                                | OF, SF, ZF, AF, PF                 |

| NEG      | Negate                          | NEG D   | $0 - (D) \rightarrow (D)$<br>1 \rightarrow (CF)          | OF, SF, ZF, AF, PF, CF             |

| DAS      | Decimal adjust for subtraction  | DAS     |                                                          | SF, ZF, AF, PF, CF<br>OF undefined |

| AAS      | ASCII adjust for<br>subtraction | AAS     |                                                          | AF, CF<br>OF, SF, ZF, PF undefined |

(a)

- Variety of arithmetic instruction provided to support integer subtraction—core instructions are

- SUB → Subtract

- SBB → Subtract with borrow

- DEC → Decrement

- NEG → Negative

- Subtract Instruction—SUB

- SUB format and operation: SUB D,S

- $(D) (S) \rightarrow (D)$

- Subtract values in two registers SUB AX,BX

- $(AX) (BX) \rightarrow (AX)$

- Subtract a value in memory and a value in a register

SUB [DI],AX

$(DS:DI) - (AX) \rightarrow (DS:DI)$

Subtract an immediate operand from a value in a register or memory SUB AX,100H

$(AX) - IMM16 \rightarrow (AX)$

Flags updated based on result

The 8088 and 8086 Microprocess GFs, DEb SFan ZFS i Aff, PF

#### 5.2 Arithmetic Instructions- Subtraction Instructions

| C:\DOS>DEBUG                                                 |                                              | a a stationar a | a an a chaire a chaire an |     |

|--------------------------------------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----|

| DS=1342 ES=1342<br>1342:0100 OF                              | CX=0000 DX=0000<br>SS=1342 CS=1342<br>DB 0F  |                                                                                                                 |                                                               |     |

| -R BX<br>BX 0000<br>:1234<br>-R CX                           |                                              |                                                                                                                 |                                                               |     |

| CX 0000<br>:0123                                             |                                              |                                                                                                                 |                                                               |     |

| -R F<br>NV UP EI PL NZ NA<br>-A                              | PONC -                                       |                                                                                                                 |                                                               |     |

| 1342:0100 SBB BX,<br>1342:0102<br>-R                         | CX                                           |                                                                                                                 |                                                               |     |

| AX=0000 BX=1234<br>DS=1342 ES=1342<br>1342:0100 19CB         | CX=0123 DX=0000<br>SS=1342 CS=1342<br>SBB BX | IP=0100 NV 0                                                                                                    | DOO SI=0000 D<br>JP EI PL NZ NA                               |     |

| -U 100 101<br>1342:0100 19CB<br>-T                           | SBB BX,                                      | , CX                                                                                                            |                                                               | . i |

| AX=0000 BX=1111<br>DS=1342 ES=1342<br>1342:0102 B98AFF<br>-Q | CX=0123 DX=0000<br>SS=1342 CS=1342<br>MOV CX | IP=0102 NV 1                                                                                                    | 000 SI=0000<br>JP EI PL NZ NA                                 |     |

| C:\DOS>                                                      |                                              |                                                                                                                 |                                                               |     |

|                                                              |                                              |                                                                                                                 |                                                               |     |

- Subtract with borrow instruction—SBB

- SBB format and operation: SBB D,S

- $(D) (S) (CF) \rightarrow (D)$

- Used for extended subtractions

- Subtracts two registers and carry (borrow)

SBB AX,BX Example:

- SBB BX,CX

- (BX) = 1234H

- (CX) = 0123H

- (CF) = 0

- $(BX) (CX) (CF) \rightarrow (BX)$

- 1234H 0123H 0H = 1111H

- (BX) = 1111H

- What about CF?

### 5.2 Arithmetic Instructions- Subtraction Instructions

| C:\DOS>DEBUG<br>-R BX<br>BX 0000<br>:3A<br>-A                |                                                                                                                   |

|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| 1342:0100 NEG BX<br>1342:0102<br>-R BX<br>BX 003A<br>:       |                                                                                                                   |

| -U 100 101<br>1342:0100 F7DB<br>-T                           | NEG BX                                                                                                            |

| AX=0000 BX=FFC6<br>DS=1342 ES=1342<br>1342:0102 B98AFF<br>-Q | CX=0000 DX=0000 SP=FFEE BP=0000 SI=0000 DI=0000<br>SS=1342 CS=1342 IP=0102 NV UP EI NG NZ AC PE CY<br>MOV CX,FF8A |

C:\DOS>

Negate instruction—NEG

- NEG format and operation

NEG D

(0) (D) → (D)

- (1)→ (CF)

- Example:

- **NEG BX**

- (BX) =003AH

- $(0) (\mathsf{BX}) \rightarrow (\mathsf{BX})$

- 0000H 003AH=

- 0000H + FFC6H (2's complement) = FFC6H

- (BX) =FFC6H; CF =1

- **Decrement instruction—DEC**

- DEC format and operation DEC D

$(D) - 1 \rightarrow (D)$

- Used to decrement pointer—addresses

- Example

DEC SI

(SI) = 0FFFH

(SI) 1 → SI

**OFFFH - 1 = OFFEH** The 8088 and 8086 Microprocessors Triebel and Singh (DI) = OFFEH

# 5.2 Arithmetic Instructions- Multiplication Instructions

| Mnemonic | Meaning                        | Format | Operation                                                                                                                                                                                                        | Flags Affected                      |

|----------|--------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| MUL      | Multiply<br>(unsigned)         | MUL S  | $(AL) \cdot (S8) \rightarrow (AX)$<br>$(AX) \cdot (S16) \rightarrow (DX), (AX)$                                                                                                                                  | OF, CF<br>SF, ZF, AF, PF undefined  |

| DIV      | Division<br>(unsigned)         | DIV S  | (1) Q((AX)/(S8)) → (AL)<br>R((AX)/(S8)) → (AH)                                                                                                                                                                   | OF, SF, ZF, AF, PF, CF<br>undefined |

|          |                                |        | (2) $Q((DX,AX)/(S16)) \rightarrow (AX)$<br>$R((DX,AX)/(S16)) \rightarrow (DX)$<br>If Q is FF <sub>16</sub> in case (1) or<br>FFFF <sub>18</sub> in case (2), then<br>type 0 interrupt occurs                     |                                     |

| IMUL     | Integer multiply<br>(signed)   | IMUL S | $(AL) \cdot (S8) \rightarrow (AX)$<br>$(AX) \cdot (S16) \rightarrow (DX),(AX)$                                                                                                                                   | OF, CF<br>SF, ZF, AF, PF undefined  |

| IDIV     | Integer divide<br>(signed)     | IDIV S | (1) Q((AX)/(S8)) → (AL)<br>R((AX)/(S8)) → (AH)                                                                                                                                                                   | OF, SF, ZF, AF, PF, CF<br>undefined |

|          |                                |        | (2) Q((DX,AX)/(S16)) → (AX)<br>R((DX,AX)/(S16)) → (DX)<br>If Q is positive and exceeds<br>7FFF <sub>16</sub> or if Q is negative<br>and becomes less than<br>8001 <sub>16</sub> , then type 0 interupt<br>occurs | 1.                                  |

| AAM      | Adjust AL for                  | AAM    | Q((AL)/10) → (AH)                                                                                                                                                                                                | SF, ZF, PF                          |

|          | multiplication                 | -      | R((AL)/10) → (AL)                                                                                                                                                                                                | OF, AF, CF undefined                |

| AAD      | Adjust AX for<br>division      | AAD    | $(AH) \cdot 10 + (AL) \rightarrow (AL)$<br>$00 \rightarrow (AH)$                                                                                                                                                 | SF, ZF, PF<br>OF, AF, CF undefined  |

| CBW      | Convert byte to<br>word        | CBW    | (MSB of AL) $\rightarrow$ (All bits of AH)                                                                                                                                                                       | None                                |

| CWD      | Convert word to<br>double word | CWD    | (MSB of AX) $\rightarrow$ (All bits of DX)                                                                                                                                                                       | None                                |

(a)

(b)

- Integer multiply instructions—MUL and IMUL

- Multiply two unsigned or signed byte or word operands

- General format and operation MUL S = Unsigned integer multiply IMUL S = Signed integer

- multiply (AL) X (S8)  $\rightarrow$  (AX) 8-bit product gives 16 bit result (AX) X (S16)  $\rightarrow$  (DX), (AX) 16-

- bit product gives 32 bit result

- Source operand (S) can be an 8-bit or 16-bit value in a register or memory

- AX assumed to be destination for 16 bit result

- DX,AX assumed destination for 32 bit result

- Only CF and OF flags updated; other undefined

# 5.2 Arithmetic Instructions- Multiplication Instructions

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | • Example:                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C:\DOS>DEBUG<br>-R AX<br>AX 0000<br>:FF<br>-R CX<br>CX 0000<br>:FE<br>-A<br>1342:0100 MUL CL<br>1342:0102<br>-R AX<br>AX 00FF<br>:<br>-R CX<br>CX 00FF<br>:<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- | (AL) = $-1_{10}$<br>(CL) = $-2_{10}$<br>Expressing in 2's complement<br>(AL) = $-1 = 11111111_2 = FFH$<br>(CL) = $-2 = 11111110_2 = FEH$<br>Operation:<br>(AL) X (CL) → (AX) |

| 1342:0102         B98AFF         MOV         CX, FF8A         -Q           C:\DOS>         C:\DOS>         C:\DOS>         C:\DOS>         C:\DOS>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $\frac{11111111_2 \times 1111110_2 = 1111110100000010}{(AX) = FD02H}$                                                                                                        |

| Mnemonic | Meaning                                     | Format | Operation                                                                                                                                                                                                                                | Flags Affected                                            |

|----------|---------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| MUL      | Multiply<br>(unsigned)                      | MUL S  | $(AL) \cdot (S8) \rightarrow (AX)$<br>$(AX) \cdot (S16) \rightarrow (DX), (AX)$                                                                                                                                                          | OF, CF<br>SF, ZF, AF, PF undefined                        |

| DIV      | Division<br>(unsigned)                      | DIV S  | (1) Q((AX)/(S8)) → (AL)<br>R((AX)/(S8)) → (AH)                                                                                                                                                                                           | OF, SF, ZF, AF, PF, CF<br>undefined                       |

|          |                                             |        | (2) $Q((DX,AX)/(S16)) \rightarrow (AX)$<br>$R((DX,AX)/(S16)) \rightarrow (DX)$<br>If Q is $F_{16}$ in case (1) or<br>$FFF_{16}$ in case (2), then<br>type 0 interrupt occurs                                                             |                                                           |

| IMUL     | Integer multiply<br>(signed)                | IMUL S | $(AL) \cdot (S8) \rightarrow (AX)$<br>$(AX) \cdot (S16) \rightarrow (DX),(AX)$                                                                                                                                                           | OF, CF<br>SF, ZF, AF, PF undefined                        |

| IDIV     | Integer divide<br>(signed)                  | IDIV S | (1) $Q((AX)/(S8)) \rightarrow (AL)$<br>$R((AX)/(S8)) \rightarrow (AH)$                                                                                                                                                                   | OF, SF, ZF, AF, PF, CF<br>undefined                       |

|          |                                             |        | (2) $Q((DX,AX)/(S16)) \rightarrow (AX)$<br>$R((DX,AX)/(S16)) \rightarrow (DX)$<br>If Q is positive and exceeds<br>7FFF <sub>16</sub> or if Q is negative<br>and becomes less than<br>8001 <sub>16</sub> , then type 0 interupt<br>occurs | 5<br>                                                     |

| AAM      | Adjust AL for                               | ААМ    | Q((AL)/10) → (AH)                                                                                                                                                                                                                        | SF, ZF, PF                                                |

| AAD      | multiplication<br>Adjust AX for<br>division | AAD    | $\begin{array}{l} R((AL)/10) \to (AL) \\ (AH) \cdot 10 + (AL) \to (AL) \\ 00 \to (AH) \end{array}$                                                                                                                                       | OF, AF,CF undefined<br>SF, ZF, PF<br>OF, AF, CF undefined |

| CBW      | Convert byte to word                        | CBW    | (MSB of AL) $\rightarrow$ (All bits of AH)                                                                                                                                                                                               | None                                                      |

| CWD      | Convert word to<br>double word              | CWD    | (MSB of AX) $\rightarrow$ (All bits of DX)                                                                                                                                                                                               | None                                                      |

(a)

| Source |  |

|--------|--|

| Reg8   |  |

| Reg16  |  |

| Mem8   |  |

| Mem16  |  |

| (b)    |  |

Integer divide instructions—DIV and IDIV

Divide unsigned—DIV S

Operations:

$(AX) / (S8) \rightarrow (AL) =$ quotient

(AH) = remainder

- 16 bit dividend in AX divided by 8-bit divisor in a register or memory,

- Quotient of result produced in AL

- Remainder of result produced in AH

(DX,AX) / (S16) → (AX) =quotient (DX) = remainder

- 32 bit dividend in DX,AX divided by 16-bit divisor in a register or memory

- Quotient of result produced in AX

- Remainder of result produced in DX

• Divide error (Type 0) interrupt may

#### 5.2 Arithmetic Instructions- Convert Instructions

C:\DOS>DEBUG A:EX520.EXE -U 0 9 0D03:0000 1E PUSH DS AX,0000 0D03:0001 B80000 MOV PUSH 0D03:0004 50 AX MOV AL, A1 0D03:0005 B0A1 CBW 0D03:0007 98 0D03:0008 99 CWD 0D03:0009 CB RETF -G 5 AX=0000 BX=0000 CX=0000 DX=0000 SP=003C BP=0000 SI=0000 DI=0000 DS=0CF3 ES=0CF3 SS=0D04 CS=0D03 IP=0005 NV UP EI PL NZ NA PO NC 0D03:0005 B0A1 MOV AL,A1 ÷T AX=00A1 BX=0000 CX=0000 DX=0000 SP=003C BP=0000 SI=0000 DI=0000 DS=0CF3 ES=0CF3 SS=0D04 CS=0D03 IP=0007 NV UP EI PL NZ NA PO NC 0D03:0007 98 CBW ~T AX=FFA1 BX=0000 CX=0000 DX=0000 SP=003C BP=0000 SI=0000 DI=0000 DS=0CF3 ES=0CF3 SS=0D04 CS=0D03 IP=0008 NV UP EI PL NZ NA PO NC 0D03:0008 99 CWD  $-\mathbf{T}$ AX=FFA1 BX=0000 CX=0000 DX=FFFF SP=003C BP=0000 SI=0000 DI=0000 NV UP EI PL NZ NA PO NC DS=0CF3 ES=0CF3 SS=0D04 CS=0D03 IP=0009 RETF 0D03:0009 CB -G Program terminated normally ÷Q  $C: \DOS>$ (c)

- Convert instructions

- Used to sign extension signed numbers for division

- Operations

- CBW = convert byte to word (MSB of AL) → (all bits of AH)

- CWD = convert word to double word (MSB of AX) → (all bits of DX)

- Application:

- To divide two signed 8-bit numbers, the value of the dividend must be sign extended in AX

- Load into AL

- Use CBW to sign extend to 16 bits

- Example A1H  $\rightarrow$  AL CBW sign extends to give FFA1H  $\rightarrow$  AX CWD sign extends to give FFFFH  $\rightarrow$  DX

| 5.3 Logic Instructions- Available Instructions and their Operation |

|--------------------------------------------------------------------|

| and their Operation                                                |

| Variety of logic instructions provided to support logical          |

| computations                                                       |

| • | AND | → | Logical | AND |

|---|-----|---|---------|-----|

- OR  $\rightarrow$  Logical inclusive-OR

- XOR → Logical exclusive-OR

- NOT  $\rightarrow$  Logical NOT

- Logical AND Instruction—AND

- AND format and operation:

- AND D,S

- (S) AND (D)  $\rightarrow$  (D)

- Logical AND of values in two registers AND AX,BX

- $(AX) AND (BX) \rightarrow (AX)$

- Logical AND of a value in memory and a value in a register

- AND [DI],AX

- (DS:DI) AND (AX)  $\rightarrow$  (DS:DI)

- Logical AND of an immediate operand with a value in a register or memory

**AND AX,100H**

- (AX) AND IMM16  $\rightarrow$  (AX)

- Flags updated based on result

- CF, OF, SF, ZF, PF

- AF undefined

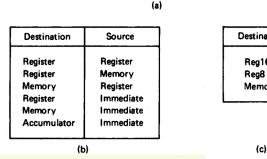

| c | Meaning              | Format  | Operation                                                   | Flags Affected                     |

|---|----------------------|---------|-------------------------------------------------------------|------------------------------------|

|   | Logical AND          | AND D,S | $(S) \cdot (D) \rightarrow (D)$                             | OF, SF, ZF, PF, CF                 |

|   | Logical Inclusive-OR | OR D,S  | $(S) + (D) \rightarrow (D)$                                 | OF, SF, ZF, PF, CF<br>AF undefined |

|   | Logical Exclusive-OR | XOR D,S | $(\mathbb{S}) \oplus (\mathbb{D}) \rightarrow (\mathbb{D})$ | OF, SF, ZF, PF, CI<br>AF undefined |

|   | Logical NOT          | NOT D   | (D) → (D)                                                   | None                               |

Mnemonia

AND

OR XOR

NOT

| Destination | Source    |             |

|-------------|-----------|-------------|

| Register    | Register  |             |

| Register    | Memory    |             |

| Memory      | Register  | Destination |

| Register    | Immediate | Destination |

| Memory      | Immediate | Register    |

| Accumulator | Immediate | Memory      |

|             |           |             |

| (           | b)        | (c)         |

- **1. Describe the AND operations.**

- 2. Describe the OR operations.

- **3. Describe the XOR operations.**

- 4. Describe the NOT operations.

#### 5.3 Logic Instructions- Example

|                                                         |                                  | C:\DOS>DEBUG<br>-A<br>1342:0100 MOV AL,55<br>1342:0102 AND AL,1F<br>1342:0104 OR AL,C0<br>1342:0106 XOR AL,OF                                                                       |

|---------------------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction                                             | (AL)                             | 1342:0108 NOT AL<br>1342:010A<br>-T                                                                                                                                                 |

| MOV AL,01010101B<br>AND AL,00011111B<br>OR AL,11000000B | 01010101<br>00010101<br>11010101 | AX=0055 BX=0000 CX=0000 DX=0000 SP=FFEE BP=0000 SI=0000 DI=0000<br>DS=1342 ES=1342 SS=1342 CS=1342 IP=0102 NV UP EI PL NZ NA PO NC<br>1342:0102 241F AND AL,1F<br>-T                |

| XOR AL,000011118<br>NOT AL                              | 11011010<br>00100101             | AX=0015 BX=0000 CX=0000 DX=0000 SP=FFEE BP=0000 SI=0000 DI=0000<br>DS=1342 ES=1342 SS=1342 CS=1342 IP=0104 NV UP EI PL NZ NA PO NC<br>1342:0104 0CC0 OR AL, C0<br>-T                |

|                                                         |                                  | AX=00D5 BX=0000 CX=0000 DX=0000 SP=FFEE BP=0000 SI=0000 DI=0000<br>DS=1342 ES=1342 SS=1342 CS=1342 IP=0106 NV UP EI NG NZ NA PO NC<br>1342:0106 340F XOR AL,0F<br>-T                |

|                                                         |                                  | AX=00DA BX=0000 CX=0000 DX=0000 SP=FFEE BP=0000 SI=0000 DI=0000<br>DS=1342 ES=1342 SS=1342 CS=1342 IP=0108 NV UP EI NG NZ NA PO NC<br>1342:0108 F6D0 NOT AL<br>-T                   |

|                                                         |                                  | AX=0025 BX=0000 CX=0000 DX=0000 SP=FFEE BP=0000 SI=0000 DI=0000<br>DS=1342 ES=1342 SS=1342 CS=1342 IP=010A NV UP EI NG NZ NA PO NC<br>1342:010A 2B04 SUB AX,[SI] DS:0000=20CD<br>-Q |

|                                                         |                                  | C:\DOS>                                                                                                                                                                             |

The 8088 and 8086 Microprocessors, Triebel and Singh

32

#### 5.3 Logic Instructions- Mask Application

- Application— Masking bits with the logic instructions

- Mask—to clear a bit or bits of a byte or word to 0

- AND operation can be used to perform the mask operation

- 1 AND 0  $\rightarrow$  0; 0 and 0  $\rightarrow$  0

- A bit or bits are masked by ANDing with 0

- 1 AND 1  $\rightarrow$  1; 0 AND 1  $\rightarrow$  0

- ANDing a bit or bits with 1 results in no change

- Example: Masking the upper 12 bits of a value in a register AND AX,000FH

- (AX) =FFFF

IMM16 AND  $(AX) \rightarrow (AX)$

000FH AND FFFFH =  $000000000001111_2$  AND  $111111111111111_2$

= 00000000001111<sub>2</sub>

= 000FH

**1. Write an AND instruction to clear the 5th bit in the AL.**

(AL) = b7b6b5b4b3b2b1b0?

#### 5.3 Logic Instructions- Mask Application

• OR operation can be used to set a bit or bits of a byte or word to 1

- X OR 0  $\rightarrow$  X; result is unchanged

- X or 1  $\rightarrow$  1; result is always 1

- Example: Setting a control flag in a byte memory location to 1 MOV AL,[CONTROL\_FLAGS]

OR AL, 10H ; 00010000 sets fifth bit –b4

- MOV [CONTROL\_FLAGS],AL

General Operation:

(AL) =  $XXXXXXX_2$  OR 00010000<sub>2</sub> =  $XXX1XXX_2$

**1. What is CONTROL\_FLAGS?**

2, What is it relative to?

#### 5.4 Shift Instructions- Available Instructions

| Mnemonic | Meaning                                        | Format          | Operation                                                                                                                                                           | Flags Affected                                              |

|----------|------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| SAL/SHL  | Shift arithmetic<br>left/shift<br>logical left | SAL/SHL D,Count | Shift the (D) left by the number<br>of bit positions equal to Count<br>and fill the vacated bits positions<br>on the right with zeros                               | CF, PF, SF, ZF<br>AF undefined<br>OF undefined if count ≠ 1 |

| SHR      | Shift logical<br>right                         | SHR D,Count     | Shift the (D) right by the number<br>of bit positions equal to Count<br>and fill the vacated bit positions<br>on the left with zeros                                | CF, PF, SF, ZF<br>AF undefined<br>OF undefined if count ≠ 1 |

| SAR      | Shift arithmetic right                         | SAR D,Count     | Shift the (D) right by the number<br>of bit positions equal to Count<br>and fill the vacated bit positions<br>on the left with the original most<br>significant bit | SF, ZF, PF, CF<br>AF undefined<br>OF undefined if count ≠1  |

(a)

| Destination | Count |

|-------------|-------|

| Register    | 1     |

| Register    | CL    |

| Memory      | 1     |

| Memory      | CL    |

(b)

- Variety of shift instructions provided

- SAL/SHL → Shift arithmetic left/shift logical left

- SHR → Shift logical right

- SAR  $\rightarrow$  Shift arithmetic right

Perform a variety of shift left and shift right operations on the bits of a destination data operand

Basic shift instructions—SAL/SHL, SHR, SAR

- Destination may be in either a register or a storage location in memory

- Shift count may be:

- 1= one bit shift

- **CL** = 1 to 255 bit shift

- Flags updated based on result

- CF, SF, ZF, PF

- AF undefined

- OF undefined if Count ≠ 1

(a)

Note: Signed or unsigned data answer is the same

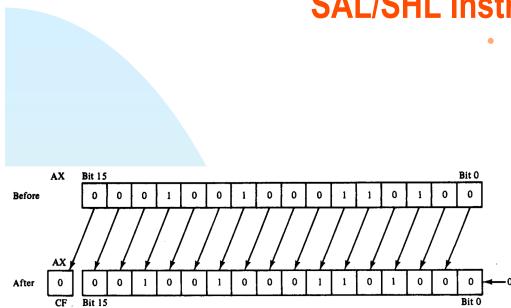

### 5.4 Shift Instructions- Operation of the SAL/SHL Instruction

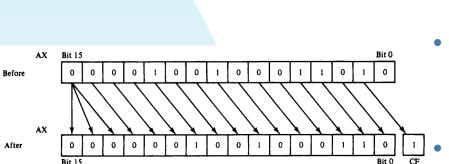

- SAL/SHL instruction operation

- Typical instruction—count of 1 SHL AX,1

- Before execution

Dest = (AX) = 1234H

$= 0001001000110100_{2}$

**Count = 1**

CF = X

- Operation

- The value in all bits of AX are shifted left one bit position

- Emptied LSB is filled with 0

- Value shifted out of MSB goes to carry flag

- After execution

Dest = (AX) = 2468H

$= 0010010001101000_{2}$

- **Conclusion**

- MSB has been isolated in CF and can be acted upon by control flow instruction– conditional jump

- Result has been multiplied by 2

(b)

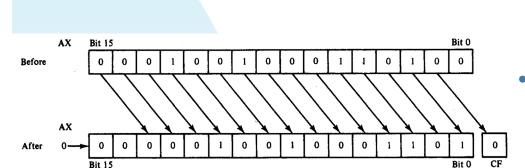

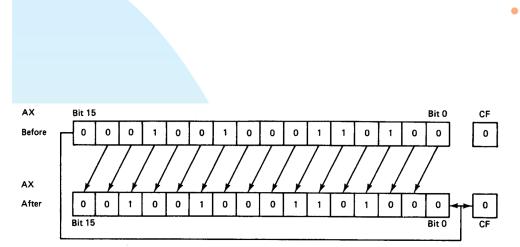

Note: processes unsigned data SHR instruction operation

- Typical instruction—count in CL SHR AX,CL

- Before execution

Dest =  $(AX) = 1234H = 4660_{10}$

$= 0001001000110100_{2}$

Count = (CL) = 02H

CF = X

Operation

- The value in all bits of AX are shifted right two bit positions

- Emptied MSBs are filled with 0s

- Value shifted out of LSB goes to carry flag

- After execution

Dest =  $(AX) = 048DH = 1165_{10}$

$= 0000010010001101_{2}$

**CF = 0**

- Conclusion

- Bit 1 has been isolated in CF and can be acted upon by control flow instruction

– conditional jump

- Result has been divided by 4

- 4 X 1165 = 4660

### 5.4 Shift Instructions- Operation of the SAR Instruction

- SAR instruction operation

- Typical instruction—count in CL SAR AX,CL

- Before execution—arithmetic implies signed numbers

Dest = (AX) = 091AH = 0000100100011010<sub>2</sub> = +2330

Count = CL = 02H

- CF = X

- Operation

- The value in all bits of AX are shifted right two bit positions

- Emptied MSB is filled with the value of the sign bit

- Values shifted out of LSB go to carry flag

After execution

Dest =  $(AX) = 0246H = 0000001001000110_2 = +582$ CF = 1

- Conclusion

- Bit 1 has been isolated in CF and can be acted upon by control flow instruction– conditional jump

- Result has been signed extended

- Result value has been divided by 4 and <u>rounded to integer</u>

- 4 X +582 = +2328

Note: processed data treated as signed number

### 5.4 Shift Instructions- SAR Instruction Execution

#### Debug execution of example

| C:\DOS>DEBUG<br>-A                                                      |                                                                             |

|-------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| 1342:0100 SAR AX,CL<br>1342:0102<br>-R AX<br>AX 0000<br>:091A           |                                                                             |

| -R CX<br>CX 0000<br>:2<br>-R F<br>NV UP EI PL NZ NA PO NC -<br>-T       |                                                                             |

| -<br>AX=0246 BX=0000 CX=0002 DX=0000<br>DS=1342 ES=1342 SS=1342 CS=1342 | SP=FFEE BP=0000 SI=0000 DI=0000<br>IP=0102 NV UP EI PL NZ AC PO CY<br>IFF8A |

C:\DOS>

#### 5.4 Shift Instructions- Application

- Application–Isolating a bit of a byte of data in memory in the carry flag

- Example:

- Instruction sequence

MOV AL, [CONTROL\_FLAGS]

- MOV CL, 04H

- SHR AL,CL

- Before execution (CONTROL\_FLAGS) = B7B6B5B4B3B2B1B0

- After execution

(AL) = 0000B7B6B5B4

(CF) = B3

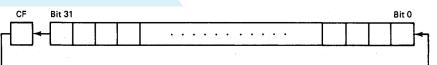

# 5.5 Rotate Instructions- Available Instructions

| Mnemonic | Meaning                       | Format      | Operation                                                                                                                                                         | Flags Affected                          |

|----------|-------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| ROL      | Rotate left                   | ROL D,Count | Rotate the (D) left by the number of bit<br>positions equal to Count. Each bit<br>shifted out from the leftmost bit goes<br>back into the rightmost bit position. | CF<br>OF undefined<br>if count ≠1       |

| ROR      | Rotate right                  | ROR D,Count | Rotate the (D) right by the number of bit<br>positions equal to Count. Each bit shifted<br>out from the rightmost bit goes into<br>the leftmost bit position.     | CF<br>OF undefined<br>if count≠1        |

| RCL      | Rotate left<br>through carry  | RCL D,Count | Same as ROL except carry is attached to (D) for rotation.                                                                                                         | CF<br>OF undefined<br>if count ≠1       |

| RCR      | Rotate right<br>through carry | RCR D,Count | Same as ROR except carry is attached to (D) for rotation.                                                                                                         | CF<br>OF undefined<br>if count $\neq 1$ |

(a)

| Destination | Count |

|-------------|-------|

| Register    | 1     |

| Register    | CL    |

| Memory      | 1     |

| Memory      | CL    |

(b)

- Variety of rotate instructions provided

- ROL  $\rightarrow$  Rotate left

- ROR  $\rightarrow$  Rotate right

- RCL → Rotate left through carry

- RCR  $\rightarrow$  Rotate right through carry

- Perform a variety of rotate left and rotate right operations on the bits of a destination data operand

- **Overview of function**

- Destination may be in either a register or a storage location in memory

- Rotate count may be:

- 1= one bit rotate

- CL = 1 to 255 bit rotate

- Flags updated based on result

- CF

- OF undefined if Count ≠ 1

- Used to rearrange information

# 5.5 Rotate Instructions- Operation of the ROL Instruction

(a)

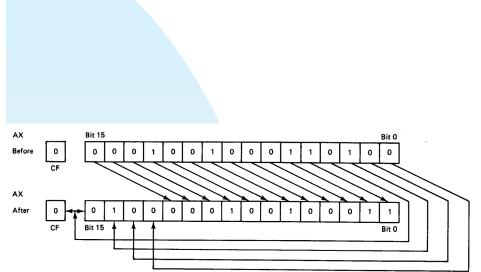

- ROL instruction operation

- Typical instruction—count of 1 ROL AX,1

- Before execution

- Dest = (AX) = 1234H

$= 0001 0010 0011 0100_{2}$

**Count = 1**

CF = 0

- Operation

- The value in all bits of AX are rotated left one bit position

- Value rotated out of the MSB is reloaded at LSB

- Value rotated out of MSB is copied to carry flag

- After execution

Dest = (AX) = 2468H

= 0010 0100 0110 1000<sub>2</sub>

(b)

# 5.5 Rotate Instructions- Operation of the ROR Instruction

- ROR instruction operation

- Typical instruction—count in CL ROR AX,CL

- Before execution

Dest = (AX) = 1234H = 0001001000110100<sub>2</sub>

- **Count = 04H**

- CF = 0

- Operation

- The value in all bits of AX are rotated right four bit positions

- Values rotated out of the LSB are reloaded at MSB

- Values rotated out of MSB copied to carry flag

- After execution

Dest = (AX) = 4123H = 0100000100100011<sub>2</sub>

- Conclusion:

- Note that the position of hex characters in AX have be rearranged

## 5.5 Rotate Instructions- Operation of the RCL Instruction

- RCL instruction operation

- Typical instruction—count in CL RCL BX,CL

- Before execution

- Dest = (BX) = 1234H = 0001001000110100<sub>2</sub>

Count = (CL) = 04H

- CF = 0

- Operation

- The value in all bits of AX are rotated left four bit positions

- Emptied MSBs are rotated through the carry bit back into the LSB

- First rotate loads prior value of CF at the LSB

- Last value rotated out of MSB retained in carry flag

- After execution

Dest =  $(BX) = 2340H = 001000110100000_2$

#### 5.5 Rotate Instructions- RCR Example

C:\DOS>DEBUG -A 1342:0100 RCR BX,CL 1342:0102 -R BX BX 0000 :1234 -R CX CX 0000 :4 -R F NV UP EI PL NZ NA PO NC - $-\mathbf{T}$ AX=0000 BX=8123 CX=0004 DX=0000 SP=FFEE BP=0000 SI=0000 DI=0000 DS=1342 ES=1342 SS=1342 CS=1342 IP=0102 OV UP EI PL NZ NA PO NC 1342:0102 B98AFF MOV CX, FF8A -Q

```

C:\DOS>

```

RCR instruction debug execution example

- Instruction—count in CL RCR BX,CL

- Before execution

Dest = (BX) = 1234H = 0001001000110100<sub>2</sub>

Count = 04H

CF = 0

- After execution

Dest = (BX) = 8123H =

1000000100100011<sub>2</sub>

CF = 0

#### 5.5 Rotate Instructions- Application

MOV AL,[HEX\_DIGITS] MOV BL,AL MOV CL,04H ROR BL,CL AND AL,0FH AND BL,0FH ADD AL,BL Disassembling and adding 2 hex digits 1<sup>st</sup> Instruction → Loads AL with byte containing two hex digits 2<sup>nd</sup> Instruction → Copies byte to BL 3<sup>rd</sup> Instruction → Loads rotate count 4<sup>th</sup> instruction → Aligns upper hex digit of BL with lower digit in AL 5<sup>th</sup> Instruction → Masks off upper hex digit in AL 6<sup>th</sup> Instruction → Masks off upper four bits of BL 7<sup>th</sup> Instruction → Adds two hex digits