#### Microprocessors B (17.384)

Spring 2011

**Lecture Outline**

**Class # 06**

March 01, 2011

**Dohn Bowden**

#### **Today's Lecture**

- Administrative

- Microcontroller Hardware and/or Interface

- Programming/Software

- Lab

- Homework

# Course Admin

#### **Administrative**

- Admin for tonight ...

- Syllabus Highlights

- Lab #2 is due March 22<sup>nd</sup>

- We shall finish Lab #2 this week and start Lab #3

- Exam #1 is next week ... March 8<sup>th</sup>

- Spring Break is the following week ... March 15<sup>th</sup>

- March 22<sup>nd</sup> will be lab #3 continuation

- Project information will be provided on March 22<sup>nd</sup>

#### **Syllabus Review**

| Week | Date     | Topics                                                                        | Lab     | Lab Report Due |

|------|----------|-------------------------------------------------------------------------------|---------|----------------|

| 1    | 01/25/11 | PIC pin out, C programming, Watchdog Timer, Sleep                             |         |                |

| 2    | 02/01/11 | General-purpose 10, LED/switch 10, FSM                                        | 1       |                |

| 3    | 02/08/11 | Lab                                                                           | 1 con't |                |

| 4    | 02/15/11 | Interrupts, Timers, interrupt-driven 10                                       | 2       |                |

| 5    | 02/22/11 | Lab                                                                           | 2 con't | 1              |

| 6    | 03/01/11 | Asynchronous and Synchronous Serial IO (UART, I <sup>2</sup> C, SPI)          | 3       |                |

| 7    | 03/08/11 | Examination 1                                                                 |         |                |

| X    | 03/15/11 | No Class – Spring Break                                                       |         |                |

| 8    | 03/22/11 | Lab                                                                           | 3 con't | 2              |

| 9    | 03/29/11 | Serial EEPROM operation, DAC, DC motor control, Servos, Stepper motor control | 4       | 3              |

| 10   | 04/05/11 | Lab                                                                           | 4 con't |                |

| 11   | 04/12/11 | Advanced Hardware Topics                                                      | Project | 4              |

| 12   | 04/19/11 | Examination 2                                                                 |         |                |

| 13   | 04/26/11 | Work on Course Project                                                        | Project |                |

| 14   | 05/03/11 | Final Exam/Course Project Brief and Demonstration                             | Demo    |                |

|      |          |                                                                               |         | 5              |

#### **Chat Page**

- Still looking into what is available through the school

- More to follow as it develops

# Microcontroller Hardware and / or Interfaces

# Input / Output ...

#### Input / Output Review

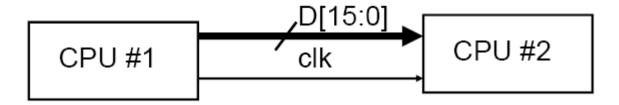

- Thus far we have looked at parallel input/output

- Data sent over a group of parallel wires

- Typically ... a clock is used for synchronization

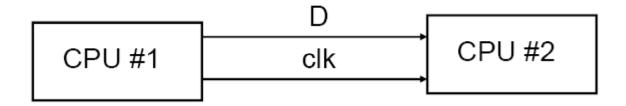

- Next ... We shall look at serial input/output

- Data sent one bit at a time, over a single wire

- A clock may or may not be used for synchronization

#### Parallel and Serial Input / Output

• Parallel ...

• Serial ...

#### Parallel vs. Serial IO

#### Parallel IO Pros/Cons

Pros: Speed, can increase bandwidth by either making data channel wider or increasing clock frequency

Cons: Expensive (wires cost money!). Short distance only – long parallel wire causes crosstalk, data corruption.

#### Serial IO Pros/Cons

Pros: Cheap, very few wires needed. Good for long distance interconnect.

Cons: Speed; the fastest serial link will typically have lower bandwidth than the fastest parallel link. However, for long distances (meters), new fast serial IO standards (USB2, Firewire) have replaced older parallel IO standards.

#### **Baud Rate vs Bits Per Second**

- Baud rate is the rate at which signaling events are sent

- Bits per second (bps) is ...

- The number of bits transferred per second ...

- any type of bits ... data ... or ... overhead bits

#### **Baud Rate vs Bits Per Second**

- If only a '1' or '0' is sent for each signaling event ... then ...

- baud rate = bps

- A signaling protocol that transfers multiple bits per signaling event ... i.e. ...

- use 4 different voltage levels, send two bits of data per signaling event (00 = -15v, 01= -5v, 10=+5v, 11 = 5v)

- In this case ... bit rate will be double the baud rate

- The effective data rate is the rate at which data is transferred, minus the overhead bits (ie. start and stop bits)

# Serial Buses ...

#### **Serial Buses**

- Serial buses can be either ...

- Asynchronous ... or ... synchronous

- Asynchronous serial connection ...

- Data is sent without using a common timing clock signal

- Synchronous serial connection ...

- Typically uses a separate clock signal to synchronize the receiver with the sender

#### **Asynchronous Serial Connection**

- To align the receiver with the sender ...

- There is some sort of start condition ...

- To signify when the transmission begins ... and ...

- A stop condition ...

- To indicate the end of transmission.

#### **Synchronous Serial Connection**

- A synchronous serial connection typically uses a separate clock signal to synchronize the receiver with the sender

- Synchronous connections may also use a start and stop condition to synchronize the receiver and sender ...

- After which the sender must send characters one right after the other

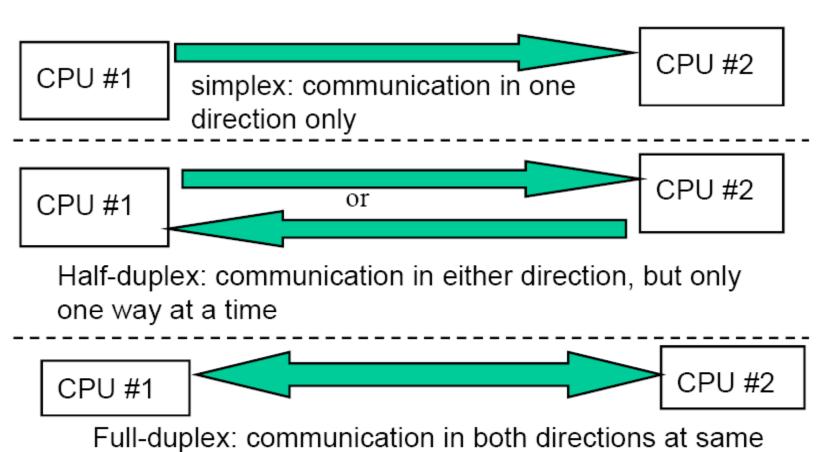

- A serial interface that can send and receive data at the same time is called full-duplex. A serial interface that must alternate between sending and receiving data is called half-duplex.

#### **Types of Serial Connections**

- Full-Duplex ...

- A serial interface that can send and receive data at the same time

- Half-Duplex ...

- A serial interface that must alternate between sending and receiving data

- Simplex ...

- Communication in one direction only

#### **Types of Serial Connections**

# PIC24 Serial On-Chip Peripherals ...

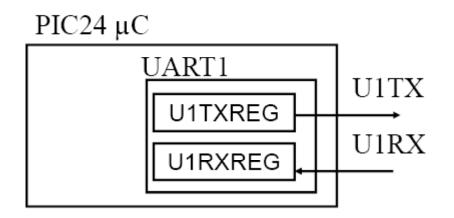

#### PIC24 Serial On-Chip Peripherals

- UART ...

- Universal Asynchronous Receiver Transmitter

- Pronounced … "you-art"

- RS-232 Standard

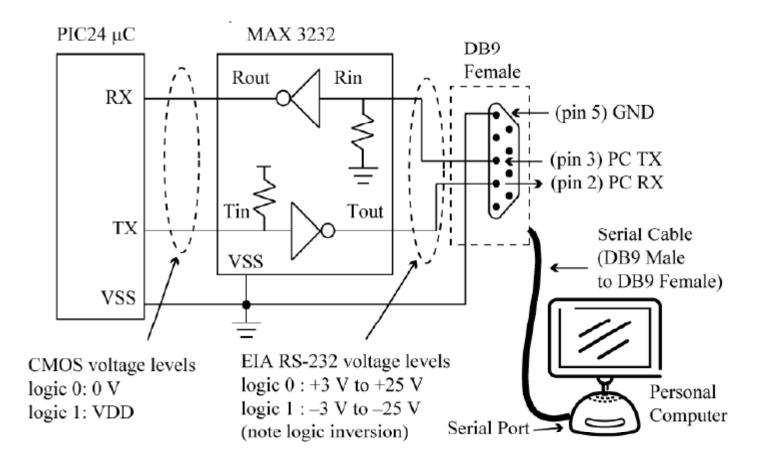

- Requires a driver to convert between RS-232 logic levels and CMOS logic levels

#### PIC24 Serial On-Chip Peripherals

- SPI ...

- Serial Peripheral Interface

- Pronounced ... "spy"

- I<sup>2</sup>C Bus ...

- Inter-Integrated Circuit

- Pronounced ... "eye squared see"

## UART ...

#### **UART**

- UART ... Universal Asynchronous Receiver Transmitter

- Hardware module that implements asynchronous serial IO

- Referred to as UARTx...

- As there may be multiple UART modules on one PIC24  $\mu$ C

- Frees the processor from having to implement software delay loops ...

- Receive/transmit done by UART while processor can do other tasks

#### **UART**

Will always use 8-bit no parity for PIC24 asynchronous serial

IO

### RS-232 ...

#### **RS-232**

- RS-232 ... Recommended Standard 232

- The traditional name for a series of standards for ...

- Serial binary single-ended data ... and... control signals connecting between ...

- a DTE (Data Terminal Equipment ... and ...

- DCE ... Data Circuit-terminating Equipment

- Commonly used in computer serial ports

#### PIC24 μC to PC Serial Input / Output Connection

Our USB-to-Serial cable uses CMOS voltage levels. Other cables may use RS-232 voltage levels, which require conversion to CMOS levels!

#### **RS-232**

- An interface standard originally used to connect PCs to modems

- The standard defines voltage levels, cable length, connector pinouts, etc

- There are other signals in the standard beside TX, RX, Gnd

- The other signals are used for modem control (Data Carrier Detect, Ring Indicator, etc) and flow control (flow control signals are used to determine if a device is ready to accept data or not)

- We will not cover the other signals in the RS232 standard

# **SPI** ...

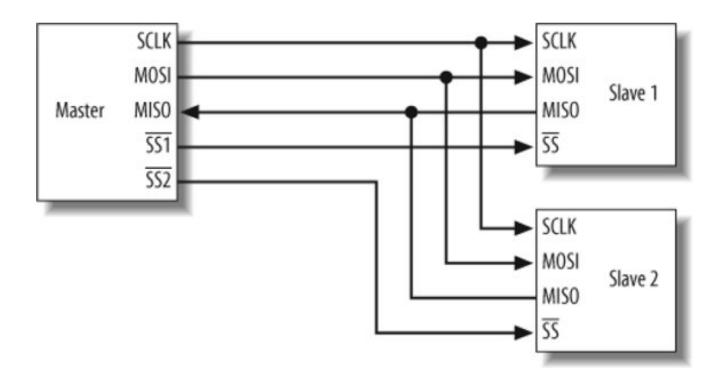

- Another serial bus that is commonly used in embedded systems is the ...

- Motorola serial peripheral interface ... SPI

- SPI can operate at data rates up to 1 Mbps

- It can operate in full-duplex mode

- Making it better suited than I<sup>2</sup>C for applications where data is constantly flowing

- I<sup>2</sup>C ...

- Uses fewer signals than SPI

- Can communicate over several feet ... a meter or more ...... and ...

- Has a well defined specification

- SPI ...

- Has a limited communication length of a few inches

- SPI does not support multiple masters ...or ... specify a device addressing scheme ...

- Therefore ... additional hardware signals are needed in order to select specific slaves

- This lack of addressing can be a benefit because it reduces the overhead in single-master, single-slave SPI interfaces

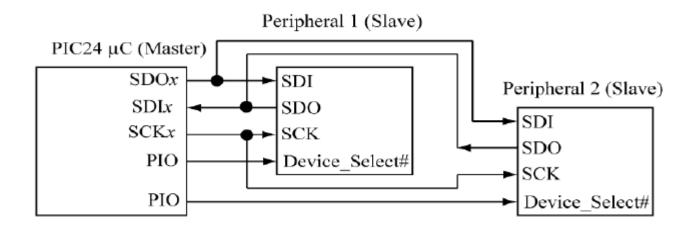

- The SPI port requires ...

- A minimum of three wires ... and ... usually 4 ... and ...

- Is technically duplex, even though most transfers are halfduplex

- Its top speed on the PIC24 μC is 10 MHz

- Best for high-speed serial transfer

- Very simple

# SPI and the I<sup>2</sup>C Comparison

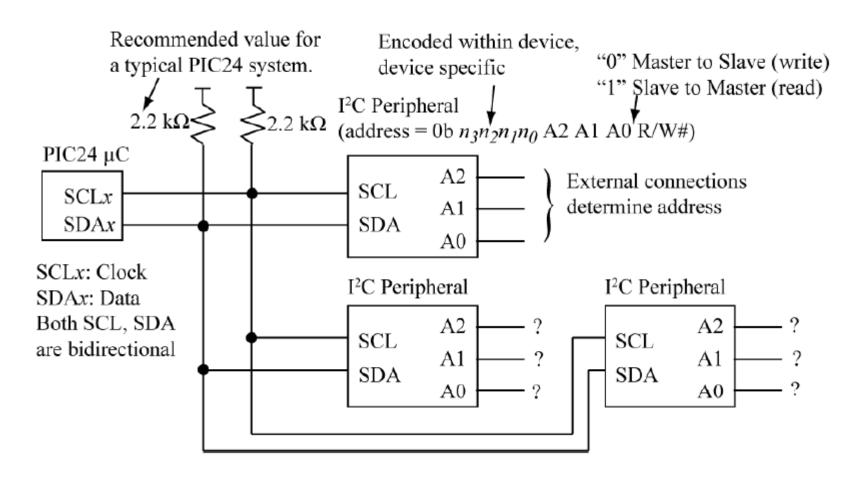

- In contrast to the SPI ... the I<sup>2</sup>C port requires ...

- Only two wires regardless of the number of peripherals

- Is half-duplex

- Top speed is 1 MHz

- Best if you are trying to reduce external pin usage

#### **SPI / PIC24 Connections**

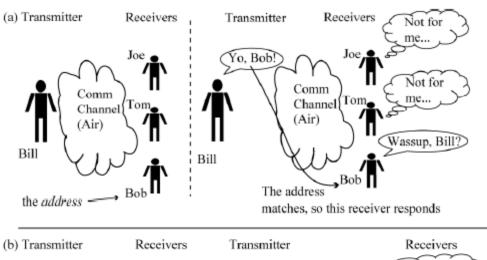

- I<sup>2</sup>C ... Inter-Integrated Circuit ...

- Pronounced "eye squared see"

- Provides a means of exchanging data between ...

- Peripheral devices ... and ... Microcontrollers ...

- Using software addressing

- Only two signals are required ...

- Data ... Clock

When a device on a bus talks, all hear what is said.

An *address* is used to specify what device the communication is intended for.

- I<sup>2</sup>C

- Does not require much in the way of hardware resources

- Ideal for ...

- Low speed

- Short distance communications

- Created by Philips

- Capable of addressing multiple devices on the same bus ...

- Up to 127 devices in Standard-mode

- 1024 in extended mode

- Various maximum data rates are supported by different revisions to the I<sup>2</sup>C specification

- These data rates are ...

- Up to 100 Kbps for Standard-mode

- 400 Kbps for Fast-mode ... and ...

- 3.4 Mbps for High-speed mode

- Devices of different data rates can be mixed on the same bus

- The I<sup>2</sup>C specification can be found online at ...

- http://www.semiconductors.philips.com

- More specifically ... (also on the course web page)

- <a href="http://ics.nxp.com/support/documents/interface/pdf/i2c.bus.specification.pdf">http://ics.nxp.com/support/documents/interface/pdf/i2c.bus.specification.pdf</a>

- Some devices that typically contain I<sup>2</sup>C bus interfaces are ...

- EEPROMs ... and ...

- Real-time clock chips

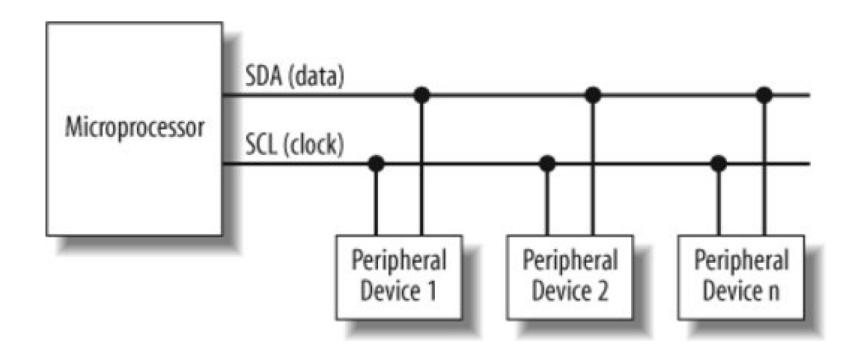

- The two I<sup>2</sup>C bus signals are ...

- Serial data (SDA) ... and ...

- Serial clock (SCL)

- The master on the bus initiates all transfers ...

- Other devices on the bus are called slaves

- On the next slide ...

- The microprocessor is the master ... and ...

- The other devices are the slaves

- Both master and slaves can receive and transmit data on the bus

- The master ...

- Initiates transactions on the bus and controls the clock signal

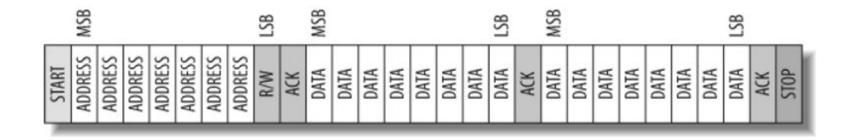

- Below is the format of an I<sup>2</sup>C bus transaction

- All data on the bus is communicated most significant bit first (MSB)

- 1. Master initiates a start condition

- 2. Master sends the 7-bit unique address of the device

- 3. Master outputs the read or write bit

- 4. Slave sends an acknowledge bit

- 5. Byte of data is exchanged followed by an acknowledgement

- Continues until all data is sent

- 6. Transaction ends with the master device causing a stop condition

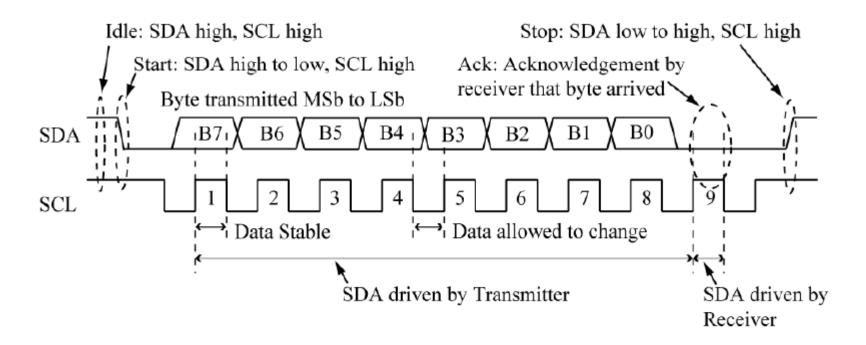

# I<sup>2</sup>C Bus Signaling

Every byte transferred takes 9 bits because of acknowledgement bit.

- 1. Master initiates a start condition

- An I<sup>2</sup>C bus data transaction begins by the master initiating a start condition

- A start condition occurs when the master causes a highto-low transition on the data line while the clock line is held high

- 2. Master sends the 7-bit unique address of the device

- 7-bit unique address of the device is sent out by the master device

- Each device on the bus checks this address with its own to determine whether the master is communicating with it

- I<sup>2</sup>C slave devices come with a predefined device address

- The lower bits of this address are sometimes configurable in hardware

- 3. Master outputs the read or write bit

- The master outputs the read or write bit

- If the bit is high ... the transaction is a read ...

- Where data goes from the slave to the master device

- If the bit is low ... the transaction is a write ...

- From the master to the slave device

- 4. Slave sends an acknowledge bit

- For the acknowledge bit ...

- The data line is kept low while the clock signal is high

- Acknowledge bits always are sent by the slave device

- 5. Byte of data is exchanged followed by an acknowledgement

- Depending on the type of transaction ... read ... or ... write

- The transmitter ... which can be slave or master ... begins sending a byte of data ... starting with the MSB

- At the end of the data byte ... the receiver ... either slave or master ... issues an acknowledge bit

- This pattern is continued until all of the data has been transferred

- 6. Transaction ends with the master device causing a stop condition

- A stop condition occurs when the master causes a low-tohigh transition on the data line while holding the clock line high

- Note that the I<sup>2</sup>C protocol supports multiple masters

#### **EEPROM** Interface

- We shall look into using the I<sup>2</sup>C bus to communicate with a serial EEPROM

- The EEPROM is the 24LC515

#### **EEPROM - 24LC515**

- Is a 64K x 8 (512K bit) Serial Electrically Erasable PROM ...

- capable of operation across a broad voltage range (1.8V to 5.5V)

- Has both byte write and page write capability of up to 64 bytes of data

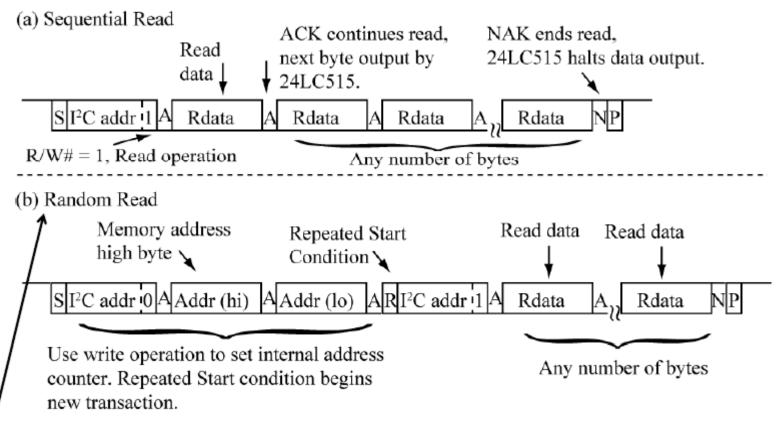

- Capable of both random and sequential reads

- Reads may be sequential within address boundaries ...

- 0000h to 7FFFh ... and ... & 8000h to FFFFh

#### **EEPROM - 24LC515**

- Functional address lines allow up to four devices on the same data bus

- This allows for up to 2 Mbits total system EEPROM memory

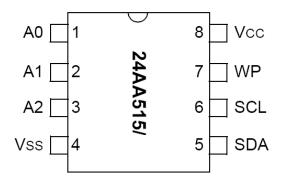

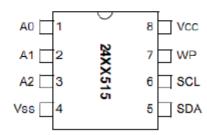

### **EEPROM - 24LC515**

TABLE 2-1: PIN FUNCTION TABLE

| Name | PDIP | SOIC | Function                                                                                                                                                                           |

|------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0   | 1    | 1    | User Configurable Chip Select                                                                                                                                                      |

| A1   | 2    | 2    | User Configurable Chip Select                                                                                                                                                      |

| A2   | 3    | 3    | Non-Configurable Chip Select.<br>This pin must be hard wired to<br>logical 1 state (Vcc). Device<br>will not operate with this pin<br>left floating or held to logical 0<br>(Vss). |

| Vss  | 4    | 4    | Ground                                                                                                                                                                             |

| SDA  | 5    | 5    | Serial Data                                                                                                                                                                        |

| SCL  | 6    | 6    | Serial Clock                                                                                                                                                                       |

| WP   | 7    | 7    | Write-Protect Input                                                                                                                                                                |

| Vcc  | 8    | 8    | +1.8 to 5.5V (24AA515)<br>+2.5 to 5.5V (24LC515)<br>+4.5 to 5.5V (24FC515)                                                                                                         |

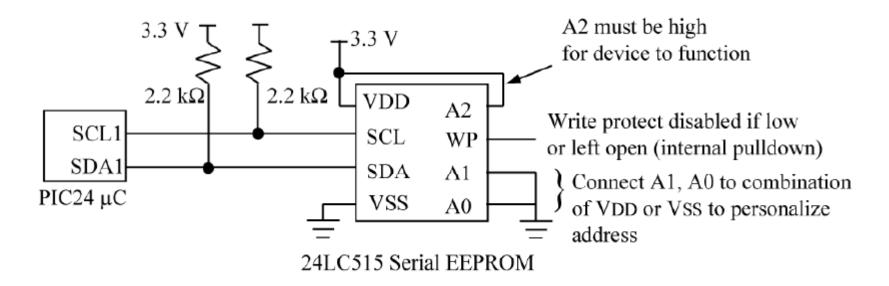

#### PIC24 μC Master to 24LC515 Serial EEPROM

EEPROM is 64 Ki x 8, internally arranged as two separate 32 Ki x 8 memories.

NOTE: The diagram above is a logical layout, not the physical pinout, shown on the right.

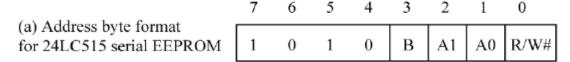

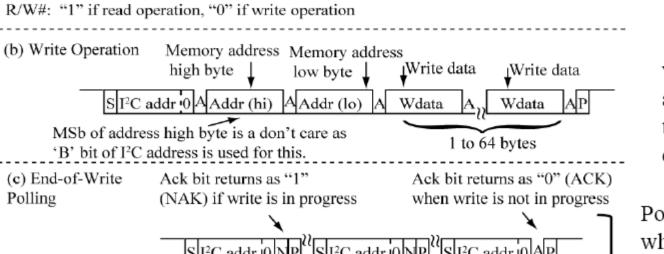

## 24LC515 I<sup>2</sup>C Address Format, Write Operation

B: Memory block select, if "0" then operation is to low memory block (0x0000-0x7FFF), if "1" then operation is to high memory block (0x8000-0xFFFF)

A1, A0: Used to personalized address, up to four LC515 EEPROMs can be on bus.

Send write command to poll for end-of-write

Most efficient to write 64 bytes at a time as write takes 3 – 5 ms to complete.

Poll device to see when the write is finished.

# 24LC515 I<sup>2</sup>C Read Operation

We will do this to read the device, and always will read 64 bytes at a time.

# Programming/Software

# **Programming/Software**

No topics for discussion

# Peer Review of Software ...

# **Peer Review of Software Developed**

- How did you write your code?

- What problems did you encountered?

- Any questions that you need resolved?

# Lab #3 ...

#### **Lab** #3

- I<sup>2</sup>C interface with a serial EEPROM

- Will write data to the EEPROM

- Then read data from the EEPROM

- Display the data on a Bar Graph display

- Could add a LCD display to perform the same function

# **Next Class**

## **Next Class Topics**

- Exam #1

- Up to ... but ... not including today's material

- March 15<sup>th</sup> ... No class Spring break

- March 22<sup>nd</sup> ... continue with Lab #3

## Homework

### Homework

- Study for Exam #1 ... next week ... March 8<sup>th</sup>

- Labs ...

- Code development for Lab #3

- Lab #2 Report ... due March 22<sup>nd</sup>

# Time to start the lab ...

## Lab

- Continue Lab #2, if needed

- Start Lab #3

## White Board ...

## References

### References

1. None